I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Constrained random verification

Constrained random verification is a testbench strategy that relies on generating pseudo-random transactions for the device under test (DUT). The goal is to reach functional coverage of a number of predefined events through random interaction with the DUT. Open Source VHDL Verification Methodology (OSVVM) is a free VHDL library which includes a number of convenient…

How to use a Case-When statement in VHDL

The Case-When statement will cause the program to take one out of multiple different paths, depending on the value of a signal, variable, or expression. It’s a more elegant alternative to an If-Then-Elsif-Else statement with multiple Elsif’s. Other programming languages have similar constructs, using keywords such as a switch, case, or select. Among other things,…

Formal verification in VHDL using PSL

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

How to use a procedure in a process in VHDL

It is possible to drive external signals from a procedure. As long as the signal is within the scope of the procedure, it can be accessed for reading or writing, even if it isn’t listed in the parameter list. Procedures that are declared in the declarative region of the architecture, cannot drive any external signals….

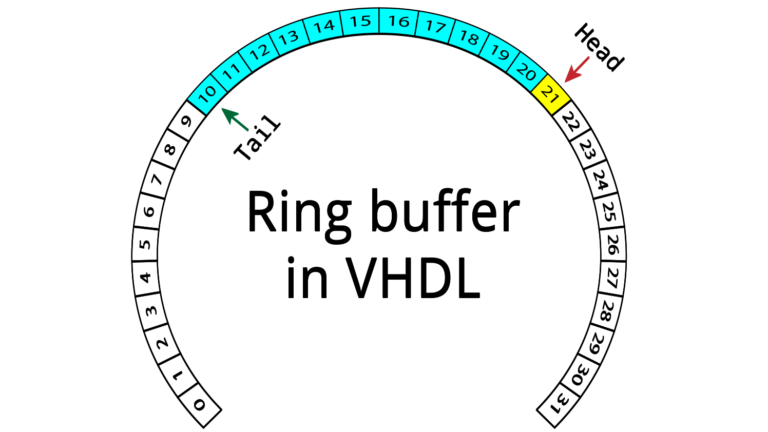

How to create a ring buffer FIFO in VHDL

Circular buffers are popular constructs for creating queues in sequential programming languages, but they can also be implemented in hardware. In this article, we will create a ring buffer in VHDL to implement a FIFO in block RAM. There are many design decisions you will have to make when implementing a FIFO. What kind of…

How to use an impure function in VHDL

An impure function can read or write any signal within its scope, also those that are not on the parameter list. We say that the function has side effects. What we mean by “side effects” is that it is not guaranteed that the function will return the same value every time it is called with…

Dear Jonas

Thanks for the content, thumbs up. please keep up the good work!

Best Regards

Thanks! That’s good to hear.

You are doing a very nice job. Top quality!

Thanks! I really appreciate your comment.

Hello Jonas

You really did save me by these great videos and materials.

These tutorials are the best thing on the internet.

Thank you for creating them.

Thanks! That’s encouraging to hear. I will do my best to keep up the quality of my blog posts.

Thank you so much man you are awesome! i learnt vhdl in university but i forgot after all years. i started again working. You help me too much! i will continue to course after this beginner course. i am planning the begin beginner fast track ! please dont stop the teaching us . thank you so much! greetings from turkey 🙂

Hello, Utku. Thank you for the nice comment! I’m glad you found my blog to be helpful. I will keep the free and premium content coming your way.

Thank you for providing such great content on a subject that imo can be tricky to really understand. But you make it easy for everyone!

That’s great to hear! I will keep on creating tutorials and articles for you. ?

Dear Jonas,

I’m an electronic engineer from Morocco, currently studying for a masters degree in microelectronics and sensors in France.

You helped me a lot to remember some of the vhdl basics and get more further into it.

I worked on an academic project using basys3 and vivado for a vga controller.

Thank you very much for this great content, keep up the good work.

I’m glad you like the quiz. It’s a good way to refresh your knowledge. 🙂

Excellent learning tool

Thanks! By the way, I also use quizzes in the VHDLwhiz membership.

Great tutorials! Short and sweet!

I’ll be sure to go onto the FPGA and VHDL Fast-Track after completing the basic tutorials..

Thanks, Dale! Also, check out the VHDLwhiz Membership, which gives you multiple courses, resource items, and coding challenges and supports your success in FPGA design.

Nice quiz, only problem is sharing your score on facebook is not working.

Thanks for the feedback. I’ve created a task on this. I’ll see if I can fix it when I have the time.