I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

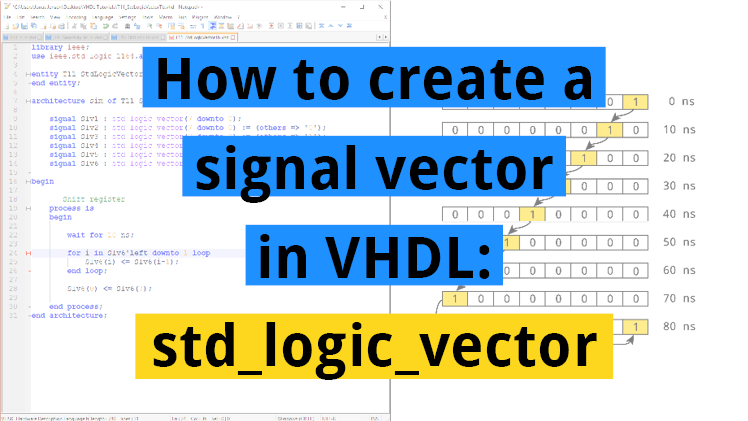

How to create a signal vector in VHDL: std_logic_vector

The std_logic_vector type can be used for creating signal buses in VHDL. The std_logic is the most commonly used type in VHDL, and the std_logic_vector is the array version of it. While the std_logic is great for modeling the value that can be carried by a single wire, it’s not very practical for implementing collections…

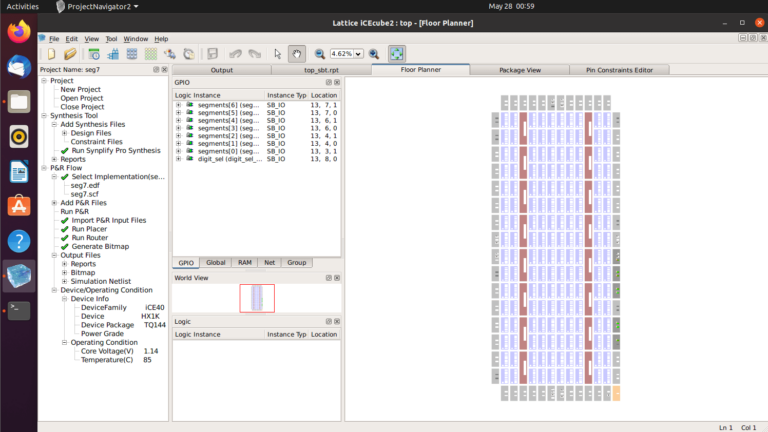

Make Lattice iCEcube2 work on Ubuntu 20.04 and program the iCEstick FPGA board

This tutorial shows how to install the Lattice iCEcube2 FPGA design software on Ubuntu 20.04. Instead of the Lattice Diamond Programmer, we will use the alternative programmer from Project IceStorm that works flawlessly on Ubuntu Linux. The Lattice iCEcube2 FPGA design software only works on Red Hat-based Linux distributions out of the box. Fortunately, we…

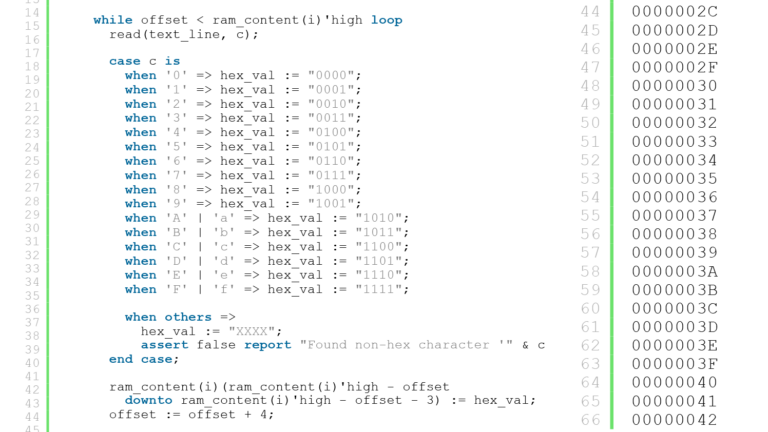

How to initialize RAM from file using TEXTIO

A convenient way to populate block RAM with initial values is to read binary or hexadecimal literals from an ASCII file. This is also a good way to create a ROM (read-only memory) in VHDL. After all, RAM and ROM are the same thing in FPGAs, ROM is a RAM that you only read from….

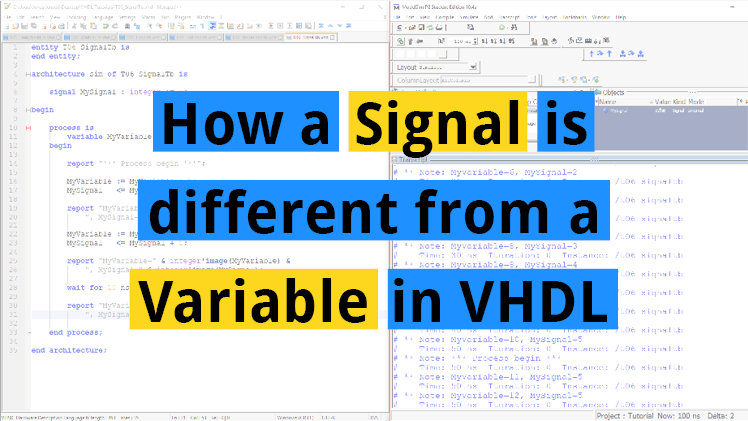

How a signal is different from a variable in VHDL

In the previous tutorial we learned how to declare a variable in a process. Variables are good for creating algorithms within a process, but they are not accessible to the outside world. If a scope of a variable is only within a single process, how can it interact with any other logic? The solution for…

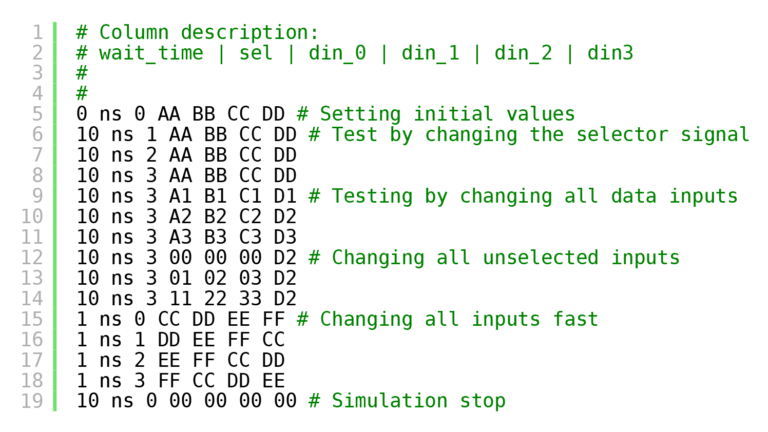

Stimulus file read in testbench using TEXTIO

Reading signal values from file is an alternative way of generating stimuli for the device on test (DUT). The testbench sequence and timing is hard-coded in a stimulus file that is read by the VHDL testbench, line by line. This allows you to easily change the pattern of the waveform that you want to feed…

How to use conditional statements in VHDL: If-Then-Elsif-Else

In the previous tutorial we used a conditional expression with the Wait Until statement. The expression ensured that the process was only triggered when the two counter signals where equal. But what if we wanted the program in a process to take different actions based on different inputs? The If-Then-Elsif-Else statements can be used to…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.