I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Formal verification in VHDL using PSL

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

Basic VHDL quiz – Part 1

Put your skills to the test with this quiz with questions from the first part of the Basic VHDL Tutorial series.

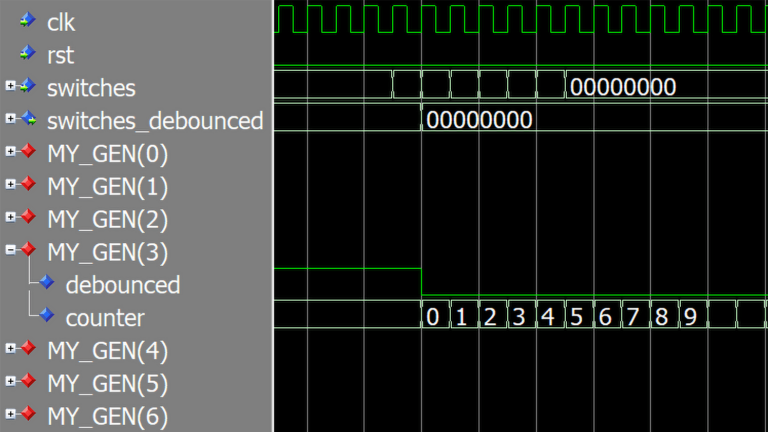

Generate statement debouncer example

The generate statement in VHDL can automatically duplicate a block of code to closures with identical signals, processes, and instances. It’s a for loop for the architecture region that can create chained processes or module instances.

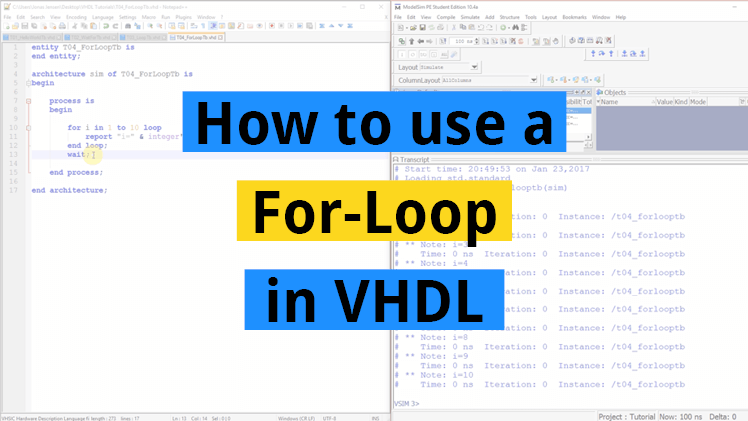

How to use a For loop in VHDL

In the previous tutorial we learned to create an infinite loop by using the loop statement. We also learned how the break out of a loop by using the exit statement. But what if we want the loop to iterate a certain number of times? The For-Loop is the easiest way to accomplish this. The…

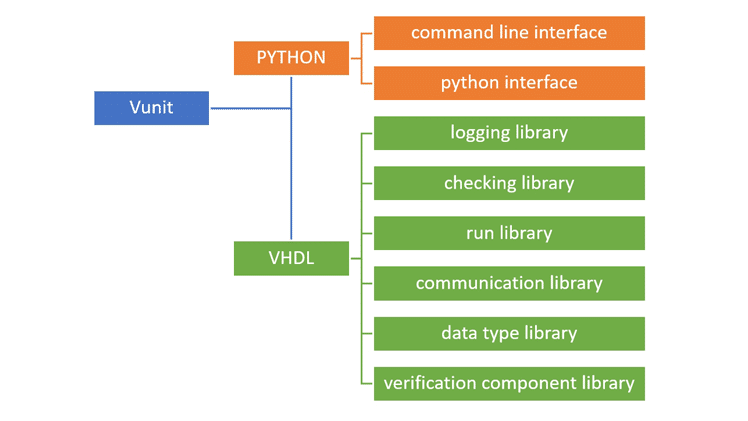

Getting started with VUnit

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

How to use a While loop in VHDL

In the previous tutorial, we learned how to use a For-Loop to iterate over an integer range. But what if we want a more detailed control of the loop than just a fixed integer range? We can use a While-Loop for this. The While-Loop will continue to iterate over the enclosed code as long as…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.