I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use conditional statements in VHDL: If-Then-Elsif-Else

In the previous tutorial we used a conditional expression with the Wait Until statement. The expression ensured that the process was only triggered when the two counter signals where equal. But what if we wanted the program in a process to take different actions based on different inputs? The If-Then-Elsif-Else statements can be used to…

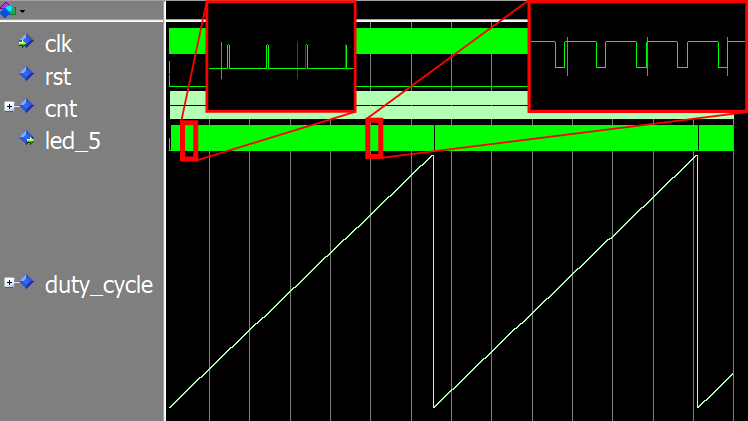

How to create a PWM controller in VHDL

Pulse-width modulation (PWM) is an efficient way to control analog electronics from purely digital FPGA pins. Instead of attempting to regulate the analog voltage, PWM rapidly switches on and off the supply current at full power to the analog device. This method gives us precise control over the moving average of energy provided to the…

How to use a procedure in VHDL

A procedure is a type of subprogram in VHDL which can help us avoid repeating code. Sometimes the need arises to perform identical operations several places throughout the design. While creating a module might be overkill for minor operations, a procedure is often what you want. Procedures can be declared within any declarative region. The…

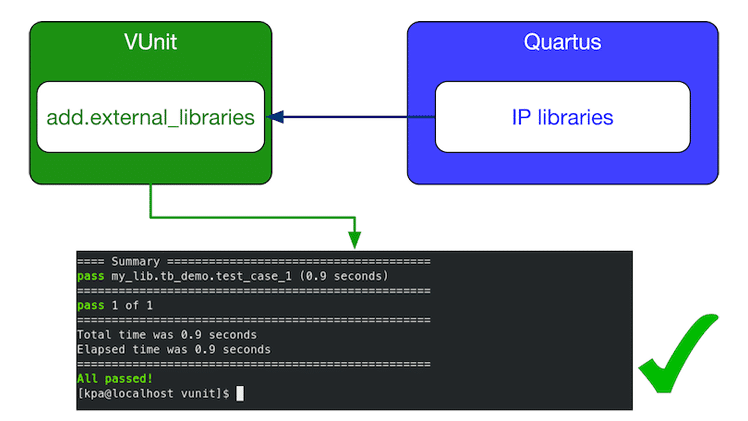

How to link Quartus Prime IP libraries to VUnit

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework?

This tutorial shows you how to generate, incorporate, and link external Quartus IP libraries to VUnit.

How to create a signal vector in VHDL: std_logic_vector

The std_logic_vector type can be used for creating signal buses in VHDL. The std_logic is the most commonly used type in VHDL, and the std_logic_vector is the array version of it. While the std_logic is great for modeling the value that can be carried by a single wire, it’s not very practical for implementing collections…

How to use a procedure in a process in VHDL

It is possible to drive external signals from a procedure. As long as the signal is within the scope of the procedure, it can be accessed for reading or writing, even if it isn’t listed in the parameter list. Procedures that are declared in the declarative region of the architecture, cannot drive any external signals….