I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Formal verification in VHDL using PSL

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

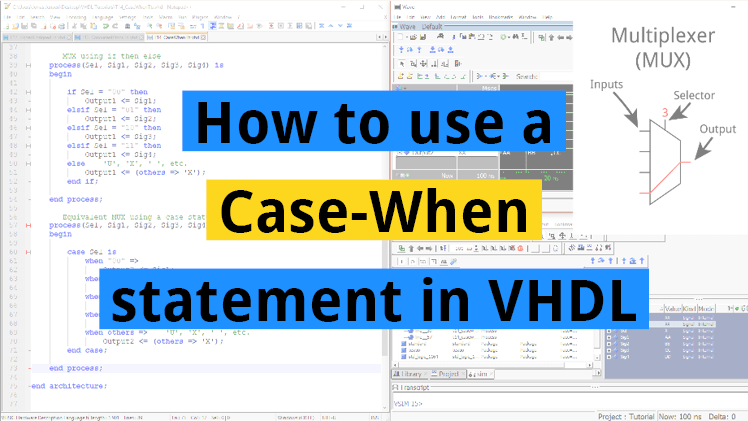

How to use a Case-When statement in VHDL

The Case-When statement will cause the program to take one out of multiple different paths, depending on the value of a signal, variable, or expression. It’s a more elegant alternative to an If-Then-Elsif-Else statement with multiple Elsif’s. Other programming languages have similar constructs, using keywords such as a switch, case, or select. Among other things,…

How to create a Tcl-driven testbench for a VHDL code lock module

Most VHDL simulators use the Tool Command Language (Tcl) as their scripting language. When you type a command in the console of the simulator, you are using Tcl. Furthermore, you can create scripts with Tcl that run in the simulator and interact with your VHDL code. In this article, we will create a self-checking testbench…

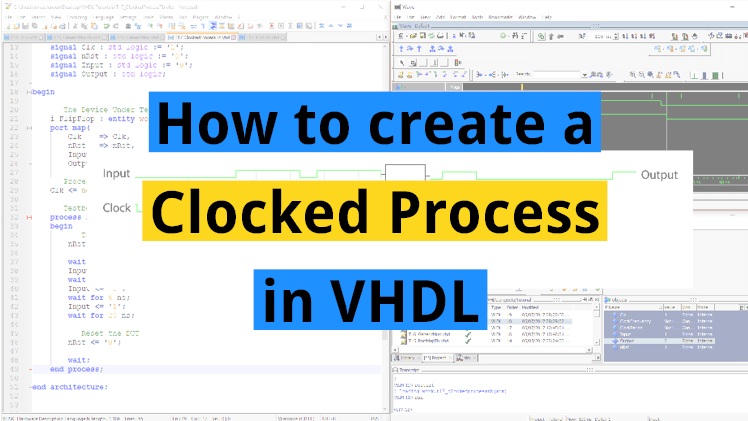

How to create a clocked process in VHDL

The vast majority of VHDL designs uses clocked logic, also known as synchronous logic or sequential logic. A clocked process is triggered only by a master clock signal, not when any of the other input signals change. The basic building block of clocked logic is a component called the flip-flop. There are different variants of…

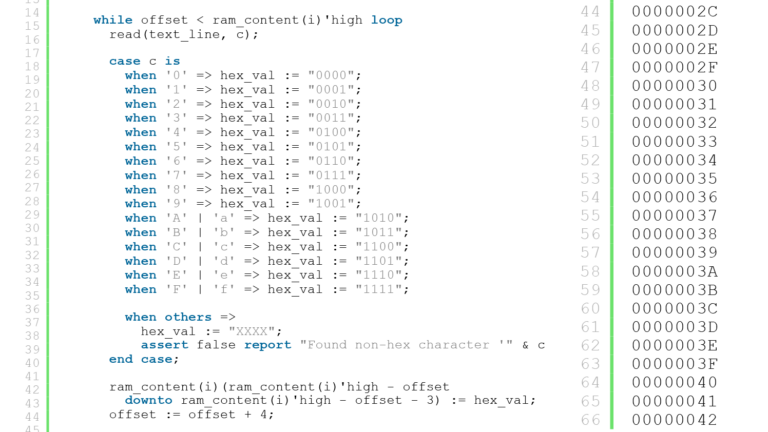

How to initialize RAM from file using TEXTIO

A convenient way to populate block RAM with initial values is to read binary or hexadecimal literals from an ASCII file. This is also a good way to create a ROM (read-only memory) in VHDL. After all, RAM and ROM are the same thing in FPGAs, ROM is a RAM that you only read from….

Basic VHDL quiz – Part 1

Put your skills to the test with this quiz with questions from the first part of the Basic VHDL Tutorial series.