I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use a Case-When statement in VHDL

The Case-When statement will cause the program to take one out of multiple different paths, depending on the value of a signal, variable, or expression. It’s a more elegant alternative to an If-Then-Elsif-Else statement with multiple Elsif’s. Other programming languages have similar constructs, using keywords such as a switch, case, or select. Among other things,…

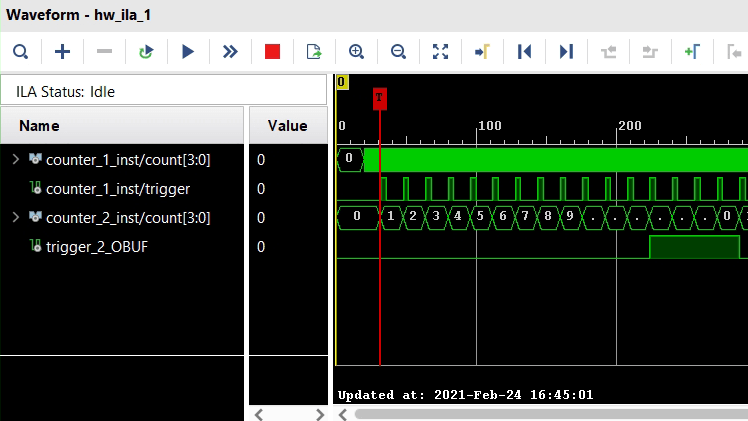

Using Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO)

This tutorial covers using the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor your VHDL design in the Xilinx Vivado IDE. In many cases, designers are in need to perform on-chip verification. That is, gaining access to an internal signal’s behavior in their FPGA design for verification purposes. One option…

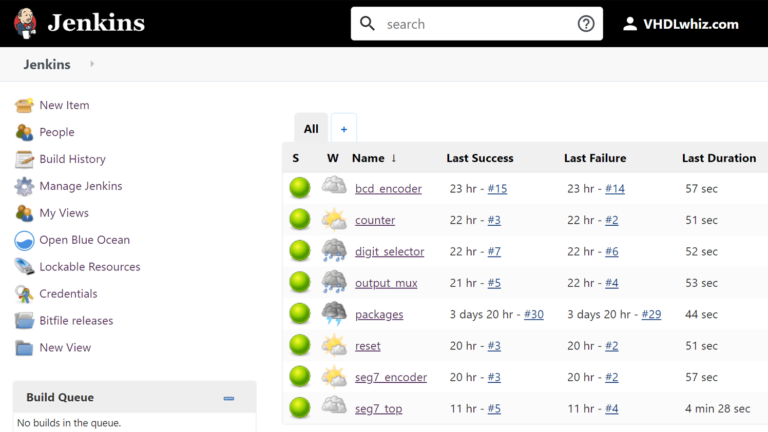

Jenkins for FPGA projects using Vivado and GitHub on a Linux VPS

This tutorial teaches you how to set up an automation server on a Virtual Private Server (VPS) using Jenkins, Xilinx Vivado, and the Git / GitHub source-control management (SCM) system.

Jenkins can be a valuable tool also for FPGA teams. Automating tasks can save your company time and improve the quality of your code. By using automatic build triggers and automated job pipelines, fewer coding errors will go unnoticed.

How to create your first VHDL program: Hello World!

When learning a new programming language, I always like to start by learning how to print. When you master outputting “Hello World!”, you know that you’ve got the environment working. It also shows you the basic skeleton of the language, the bare minimum code required to produce any output. You might be thinking: but VHDL…

How to create a Tcl-driven testbench for a VHDL code lock module

Most VHDL simulators use the Tool Command Language (Tcl) as their scripting language. When you type a command in the console of the simulator, you are using Tcl. Furthermore, you can create scripts with Tcl that run in the simulator and interact with your VHDL code. In this article, we will create a self-checking testbench…

How to use a function in VHDL

Functions are subprograms in VHDL which can be used for implementing frequently used algorithms. A function takes zero or more input values, and it always returns a value. In addition to the return value, what sets a function apart from a procedure, is that it cannot contain Wait-statements. This means that functions always consume zero…