I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use Signed and Unsigned in VHDL

The signed and unsigned types in VHDL are bit vectors, just like the std_logic_vector type. The difference is that while the std_logic_vector is great for implementing data buses, it’s useless for performing arithmetic operations. If you try to add any number to a std_logic_vector type, ModelSim will produce the compilation error: No feasible entries for…

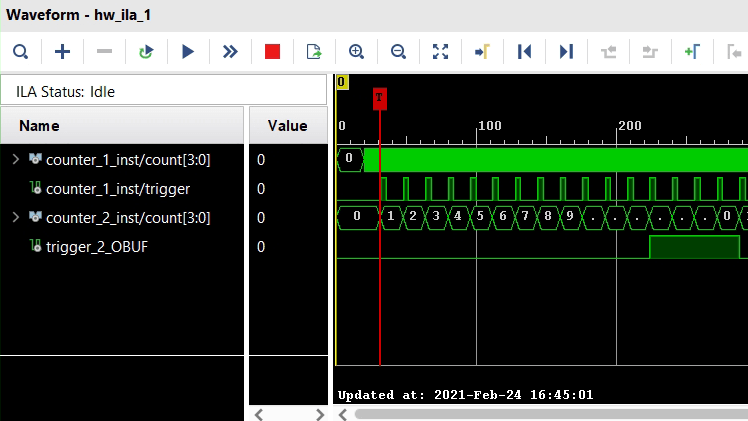

Using Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO)

This tutorial covers using the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor your VHDL design in the Xilinx Vivado IDE. In many cases, designers are in need to perform on-chip verification. That is, gaining access to an internal signal’s behavior in their FPGA design for verification purposes. One option…

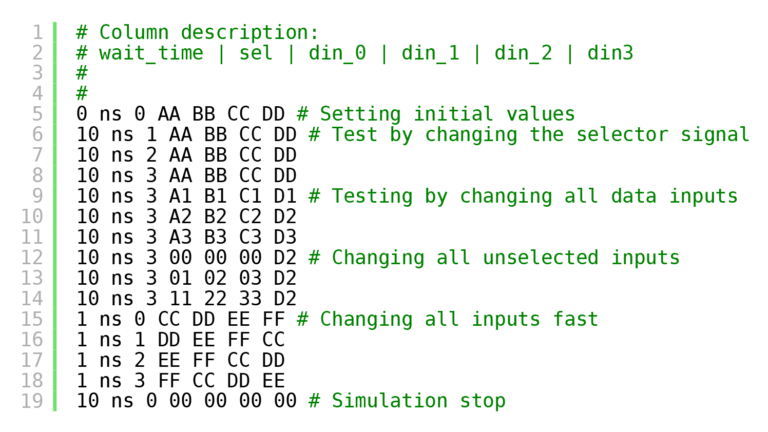

Stimulus file read in testbench using TEXTIO

Reading signal values from file is an alternative way of generating stimuli for the device on test (DUT). The testbench sequence and timing is hard-coded in a stimulus file that is read by the VHDL testbench, line by line. This allows you to easily change the pattern of the waveform that you want to feed…

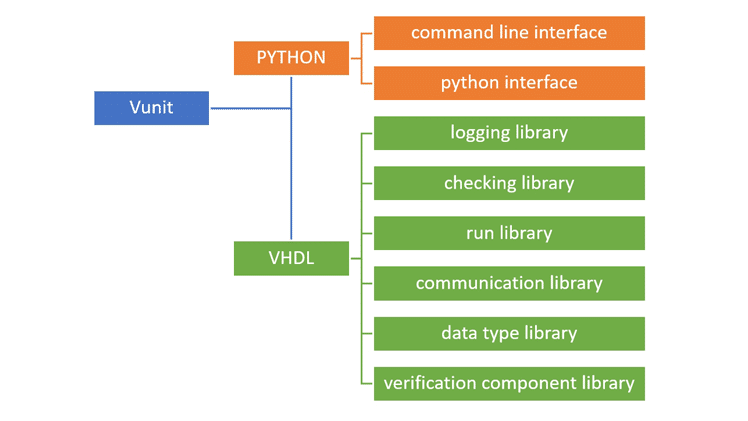

Getting started with VUnit

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

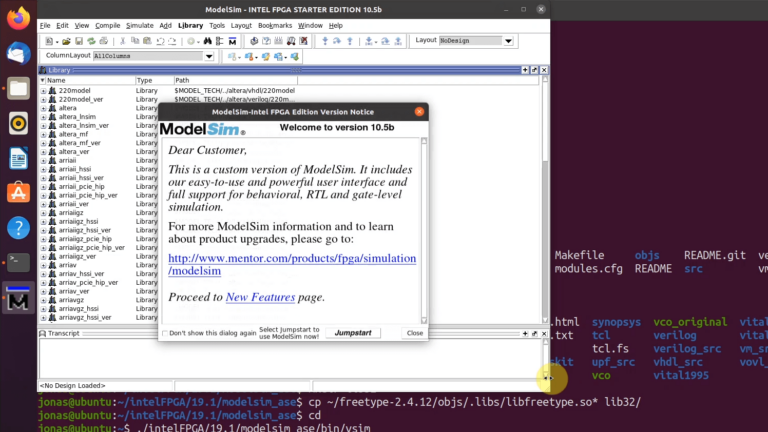

How to make ModelSim from Quartus Prime Lite work on Ubuntu 20.04

The ModelSim version that comes with Intel Quartus Prime Lite Edition is a good alternative if you want to try out VHDL simulation on your home computer. The software is available for both Windows and Linux, but Intel only supports Red Hat-based distros like CentOS Linux. Fortunately, you are just a few hacks away from…

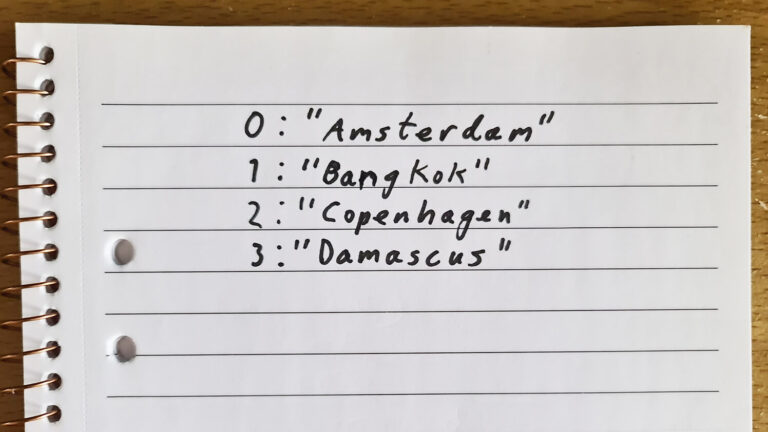

How to create a list of strings in VHDL

Text strings in VHDL are generally limited to fixed-length character arrays. That makes sense because VHDL describes hardware, and generic-length strings require dynamic memory. To define an array of strings, you have to allocate space at compile-time for the highest number of strings you want to store. And even worse, you must decide on the…

First of all, thank you so very much!

These are by far the most comprehensible tutorials I have come across like ever!

Brilliant work.

So here my two cents out of gratitude:

Basic VHDL Quiz – part 4

Which statement is not true?

Answer 3 : The return statement cannot be omitted.

-> Correct

So the return statement CAN be omitted???

“Unlike in most other programming languages, the return keyword is mandatory in functions in VHDL.”

Confused by double negation. Me or you 😉

Good catch! I’ve changed the answer now. I was trying to make you think, but in the process I confused myself too 🙂

“The return-keyword cannot be used in a procedure”. I believe that this is incorrect, e.g.

https://web.archive.org/web/20200629023040/http://vhdl.renerta.com:80/source/vhd00060.htm

It is true, of course, that you cannot return a value with it, that’s the only (?) difference between procedures and functions. But, as in other languages, you can use “return” as control flow statement to “force an exit”.

You are right! I missed the possibility of using return statements in procedures without returning a value. According to the Renata link you posted, functions must return a value, while procedures can have return statements, but then without a return value.

I am changing this question.