I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

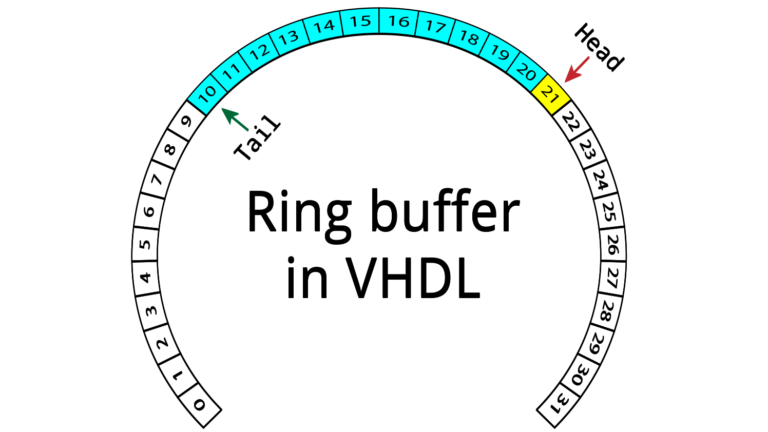

How to create a ring buffer FIFO in VHDL

Circular buffers are popular constructs for creating queues in sequential programming languages, but they can also be implemented in hardware. In this article, we will create a ring buffer in VHDL to implement a FIFO in block RAM. There are many design decisions you will have to make when implementing a FIFO. What kind of…

Basic VHDL quiz

Have fun and learn from this VHDL and FPGA design quiz with 28 questions for beginners and intermediate learners in random order.

All questions include an explanation for the correct answer that will be shown after you make your selection.

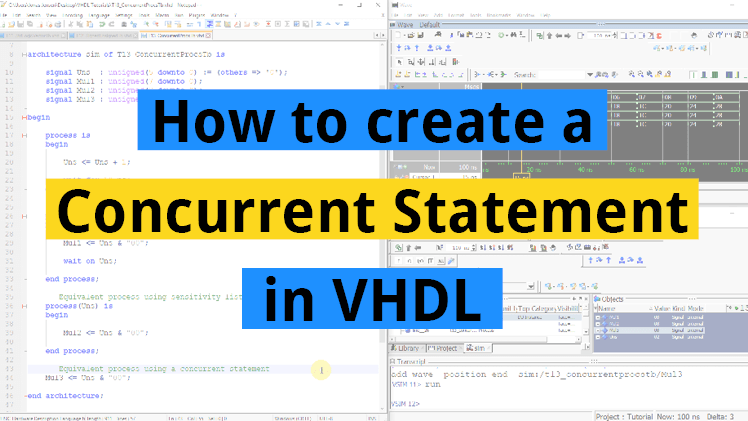

How to create a concurrent statement in VHDL

A concurrent statement in VHDL is a signal assignment within the architecture, but outside of a normal process construct. The concurrent statement is also referred to as a concurrent assignment or concurrent process. When you create a concurrent statement, you are actually creating a process with certain, clearly defined characteristics. Concurrent statements are always equivalent…

How to create a self-checking testbench

A self-checking testbench is a VHDL program that verifies the correctness of the device under test (DUT) without relying on an operator to manually inspect the output. The self-checking testbench runs entirely on its own, and prints an “OK” or “Failed” message in the end. Every VHDL module should have an associated self-checking testbench. It’s…

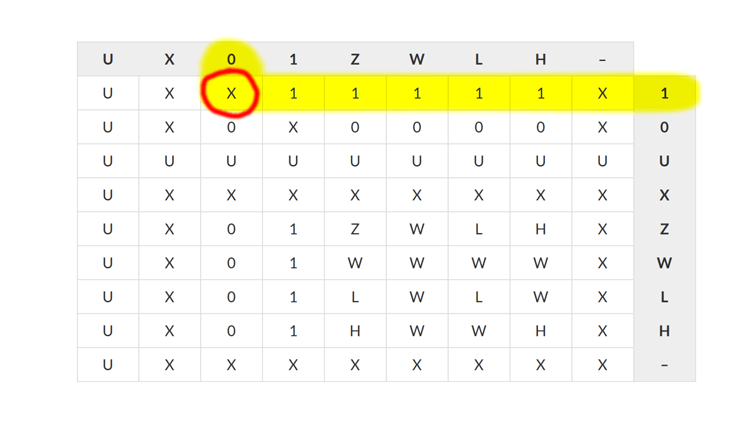

std_logic vs std_ulogic

VHDL includes few built-in types but offers several additional types through extension packages. Two of the most widely used types are std_logic and std_ulogic. The difference between them is that the former is resolved while the latter isn’t. Before we go on to investigate what it means that a type is resolved, let’s first look…

Basic VHDL quiz – Part 2

Test your coding skills with this VHDL quiz after completing tutorials 6-11 from the Basic VHDL Tutorial series!

First of all, thank you so very much!

These are by far the most comprehensible tutorials I have come across like ever!

Brilliant work.

So here my two cents out of gratitude:

Basic VHDL Quiz – part 4

Which statement is not true?

Answer 3 : The return statement cannot be omitted.

-> Correct

So the return statement CAN be omitted???

“Unlike in most other programming languages, the return keyword is mandatory in functions in VHDL.”

Confused by double negation. Me or you 😉

Good catch! I’ve changed the answer now. I was trying to make you think, but in the process I confused myself too 🙂

“The return-keyword cannot be used in a procedure”. I believe that this is incorrect, e.g.

https://web.archive.org/web/20200629023040/http://vhdl.renerta.com:80/source/vhd00060.htm

It is true, of course, that you cannot return a value with it, that’s the only (?) difference between procedures and functions. But, as in other languages, you can use “return” as control flow statement to “force an exit”.

You are right! I missed the possibility of using return statements in procedures without returning a value. According to the Renata link you posted, functions must return a value, while procedures can have return statements, but then without a return value.

I am changing this question.