I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Basic VHDL quiz – Part 2

Test your coding skills with this VHDL quiz after completing tutorials 6-11 from the Basic VHDL Tutorial series!

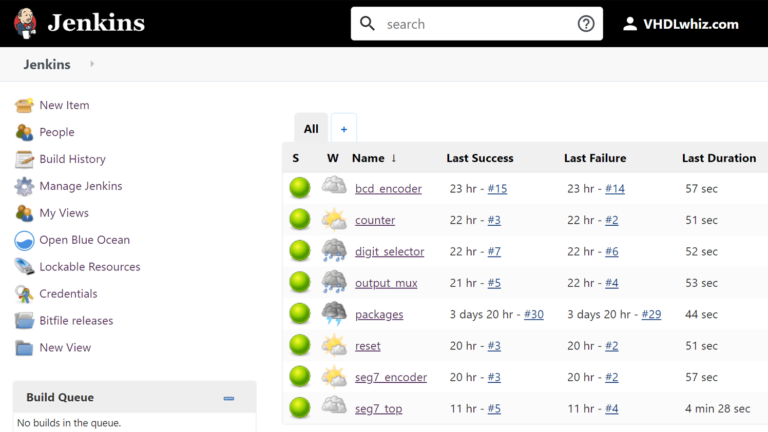

Jenkins for FPGA projects using Vivado and GitHub on a Linux VPS

This tutorial teaches you how to set up an automation server on a Virtual Private Server (VPS) using Jenkins, Xilinx Vivado, and the Git / GitHub source-control management (SCM) system.

Jenkins can be a valuable tool also for FPGA teams. Automating tasks can save your company time and improve the quality of your code. By using automatic build triggers and automated job pipelines, fewer coding errors will go unnoticed.

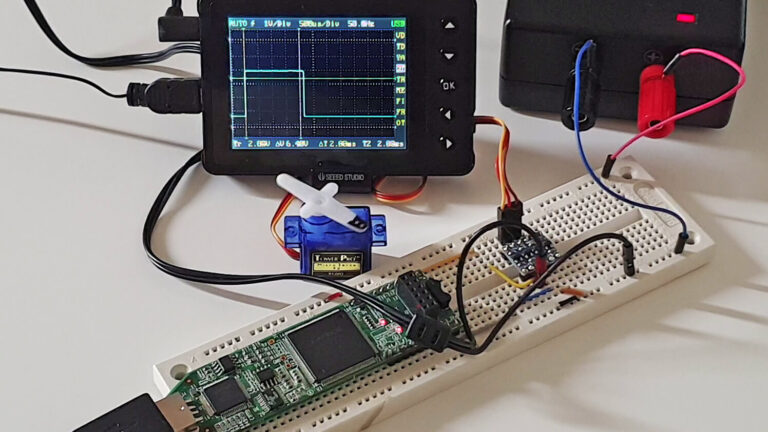

RC servo controller using PWM from an FPGA pin

Radio-controlled (RC) model servos are tiny actuators typically used in hobbyist model planes, cars, and boats. They allow the operator to control the vehicle via a radio link remotely. Because RC models have been around for a long time, the de-facto standard interface is pulse-width modulation (PWM), rather than a digital scheme. Fortunately, it’s easy…

Formal verification in VHDL using PSL

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

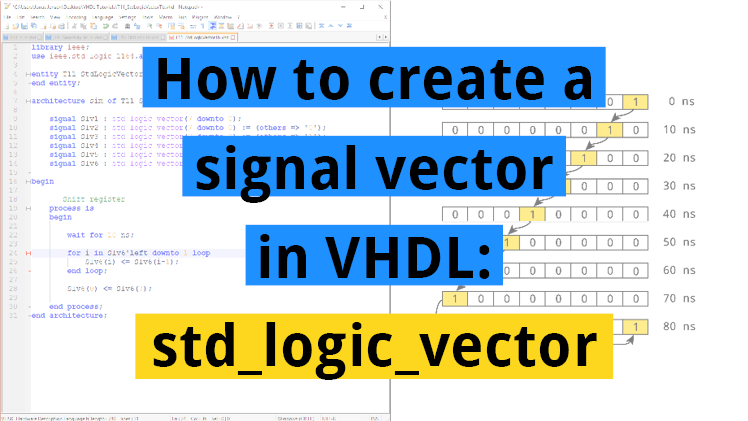

How to create a signal vector in VHDL: std_logic_vector

The std_logic_vector type can be used for creating signal buses in VHDL. The std_logic is the most commonly used type in VHDL, and the std_logic_vector is the array version of it. While the std_logic is great for modeling the value that can be carried by a single wire, it’s not very practical for implementing collections…

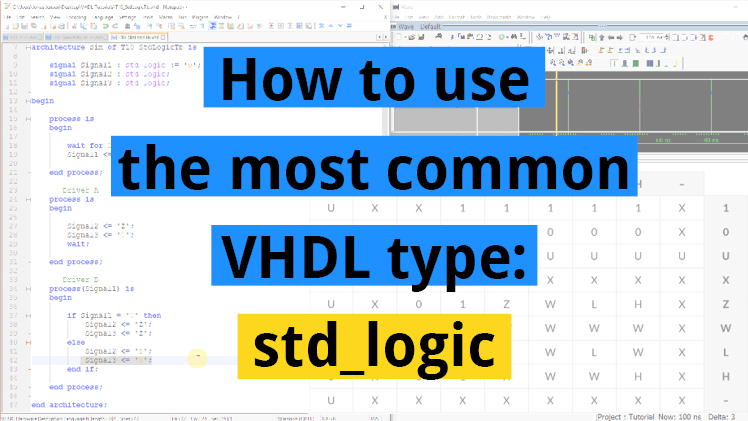

How to use the most common VHDL type: std_logic

The most common type used in VHDL is the std_logic. Think of this type as a single bit, the digital information carried by a single physical wire. The std_logic gives us a more fine-grained control over the resources in our design than the integer type, which we have been using in the previous tutorials. Normally,…