This is a guest article by Oliver Bründler, whom I (Jonas) met at the FPGA Conference Europe 2025. He is making a fantastic contribution to the community by creating an open-source VHDL library that will benefit many developers. You can learn more about him in the author box below the article.

But first, let’s hear from Oliver!

You’re designing your third FPGA project this year, and once again you find yourself writing the same FIFO implementation from scratch, just for a different device. Sound familiar?

How many hours have you spent debugging a CDC circuit that should be standard?

How often do you find yourself locked into your FPGA vendor?

These are the problems Open Logic aims to solve.

What is Open Logic?

In FPGA design, there are a wide range of rather standard functions used very often and described in many textbooks: FIFOs, clock-domain-crossings, standard interfaces and so forth. The problem in FPGA design is that in contrast to most traditional languages, there is no such thing as a standard library.

What are the options you have? Writing these elements on your own – investing effort into such basic things instead of into your application? Using macros provided by your FPGA vendor and making your code locked to this vendor?

It’s obvious that relying on some kind of open-source standard components library would be a better alternative. There are some available but it is difficult to find one that qualifies for professional use in terms of thorough documentation, true vendor independence, code quality and publicly visible CI/CD pipelines.

That’s why I decided to start the Open Logic project – and provide that “unicorn” I failed to find elsewhere: A high quality, vendor independent and professionally usable library of FPGA standard components.

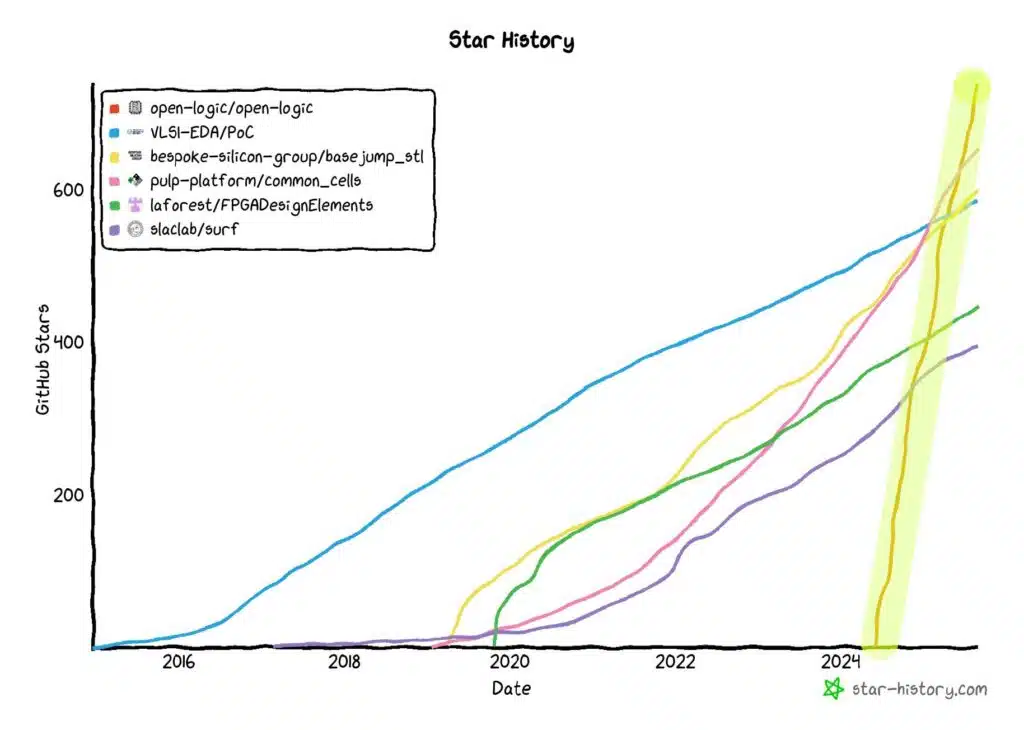

Open Logic gained traction quickly. With over 700 GitHub stars today it is among the most popular open-source FPGA libraries

The Philosophy behind Open Logic

Open Logic is not the first open source VHDL library – so you might ask yourself what makes it different and why you should use this one. The project follows the philosophy below – the decision whether this matches what you are looking for is yours.

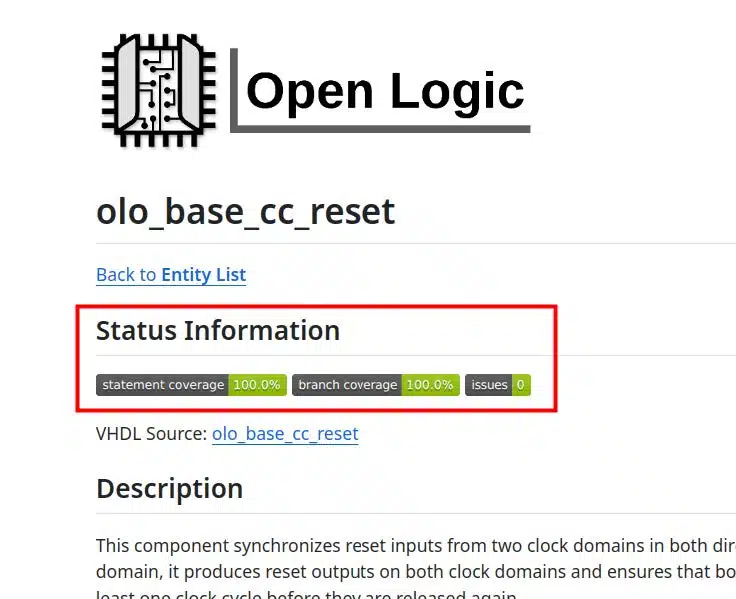

Trustable Code

Nobody wants to debug open source code he didn’t write.

Open Logic aims to provide code that can be trusted – and to provide measures for quality in the documentation of each element. Those are updated based on the results of the last CI run.

Ease of Use

Open source code should save you time – and not just redirect your time into understanding how to use it.

Open Logic does not just provide some code – but focuses on a simple user experience. This starts with good documentation for every element provided and all of its interfaces. Furthermore every optional configuration setting and port comes with a default value, so users can simply omit unused settings and ports in the instantiation, leading to concise and readable code.

One key point that gets you started very quickly with Open Logic is that there are scripts provided to integrate Open Logic in all of the supported tools (currently AMD, Altera, Microchip, Gowin, Efinix) .

Pure HDL

Only HDL is truly vendor independent.

Open Logic does not contain any vendor-specific primitives or macros. Instead, it fully relies on inference for all device resources – and it comes with a strong framework to regularly check if the inference works correctly for all tools supported. This approach ensures that Open Logic is compatible with all current and future devices and that it can naturally be compiled to any device – even the ones that are not officially supported (e.g. Lattice).

Although Open Logic is written in VHDL, it is usable from Verilog – and there is a clear commitment to preserve this situation. All interfaces are designed in a way that instantiation from Verilog is possible and Verilog tutorials are available.

Open Logic Content

The article is too short to cover content in detail. This probably will be done in follow-up articles. To get an overview over the content provided, it’s best to refer to the Entity List provided in the documentation of the Project.

Areas

In general Open Logic is organized into so-called areas:

base

Basic functionality like FIFOs, CDCs, RAMs, CAM, Delay Lines, Arbiters, CRC, etc.

axi

AXI4 masters and AXI4-Lite slave.

intf

Commonly used interfaces like SPI, I2C, UART or synchronizers.

fix

Fixed point mathematics.

Getting Started

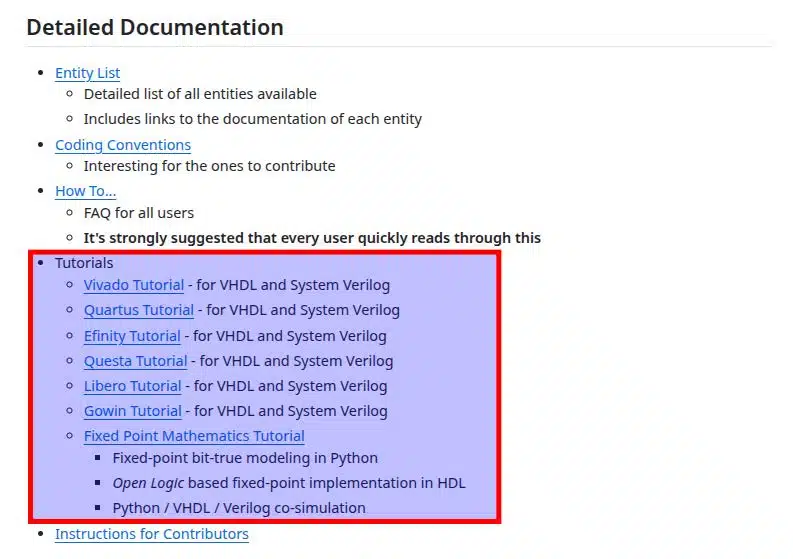

Open Logic comes with tutorials for all tools supported. Follow the tutorial for the tool you use and get your first Open Logic design running in 15 minutes!

The Tutorials can be found here.

Clone Open Logic, try it out in your projects and keep using it if you like it.

Licensing

Open Logic comes under PSI HDL License (a LGPL modified for FPGA use), which is explicitly written with commercial use in mind and it does not imply a copy-left for the project specific code using Open Logic.

Community

Open Logic is a community project. From FPGA engineers for FPGA engineers.

Support the project by giving Open Logic a star on GitHub – or even consider sponsoring the project through GitHub sponsors: https://github.com/sponsors/open-logic (every “one coffee a month” is appreciated!).

You are also welcome to contribute – with code or by simply report any problems or unclarities in the documentation.

Another way to help the project is spreading the word. Tell your friends about it, drop posts about the success you had in your Open Logic based projects and help to establish Open Logic as “common sense” to use.

Further Reading

Open Logic on GitHub

The best source of information is the documentation of Open Logic, which is provided in Markdown together with the code. You find it on the GitHub repo directly:

https://github.com/open-logic/open-logic

Open Logic on YouTube

There also is a Youtube channel available – Videos often are the best way to get into a topic:

https://www.youtube.com/@OpenLogicFPGA

On LinkedIn

I post updates on LinkedIn regularly. Follow me there to stay up to date:

https://www.linkedin.com/in/oliver-bruendler

And of course – probably there will be future Articles on VHDLWhiz – Seeing an effect of this article in terms of GitHub stars and GitHub Sponsors Donations of course increases the chance for such articles…

Hi! Thanks for a good article and intro to your project! Good luck going forward with this. The FPGA community would greatly benefit from a standard library (see: https://xkcd.com/927). 2 points/questions:

1) The color in the legend would be better if you made the color match your line (yes, yellow and red make orange, but it would be clearer with the same color in the legend).

2) Have you tried to verify the BFMs using other VCs than your own? UVVM or similar? I tried using UVVMs UART+AXI-S VVC to verify the `olo_intf_uart` (it passed). It would add to the warranted feeling if you were to add something like this to the runners, perhaps?

Hi Pelle!

Regarding XKCD: I am aware that there are other such standard libraries around (so open-logic is “+1”) – my main motivation was to create something on quality levels I feel god using professionally (key points: Vendor Inedendent, Proper Testing, Public CI, Proper Documentation) – and with this definition IMO Open Logic is pretty much unique.

I also do my best to align with maintainers of other projects (e.g. HDL-modules and PoC) so we do cover as much ground as possible together instead of everybody developing the same features.

Regarding 1) Thank you. I’ll choose the color more carefully when doing the next star-graph.

Regarding 2) For most things I use VUnit VCs (e.g. AXI4-Stream, UART) – they are not mine. Only where there is no VUnit VC (e.g. I2C) or where I need specialized VCs (AXI4 Full in the context of low-level data-transfers) I wrote my own. I may consider switching to UVVM or OSVVM at some point – it’s only the availability of development time that limits progress. I’d be very open for your contributions in this regard.