VHDLwhiz Membership

$39This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

This content from the VHDLwhiz shop is suitable for advanced users.

Showing 1–12 of 20 results

This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

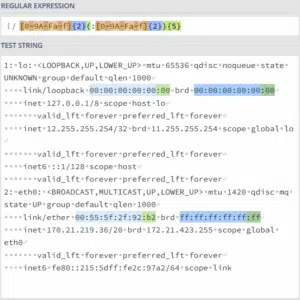

Learn to build a regex processing VHDL module with runtime-reconfigurable pattern matching and Unicode support, using AI-generated Python scripts to create configurations from regexes.

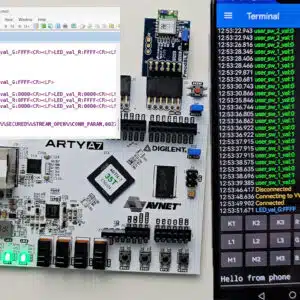

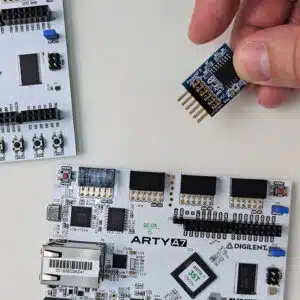

Add Bluetooth connectivity to FPGA projects! Learn to control the color LEDs on your board from a phone and show VHDL signal values in the mobile app.

Learn to create a Flash memory controller in VHDL for storing non-volatile data in FPGA projects. This course covers page program (write), read, and erase operations using the quad SPI bus.

Learn to combine VHDL configuration statements with VUnit to maximize testbench utilization and automate test cases for Wishbone bus BFM and RTL DUTs.

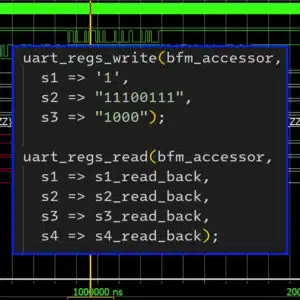

Create a bus functional model (BFM) for a VHDL module with multiple configuration options. Learn to make a system that generates custom BFMs for any interface variant the DUT can have.

Implement the classic Snake game on an FPGA with a 128×32 OLED display. Create a custom GUI to play the game in real-time using the Questa VHDL simulator.

Learn to implement constrained random testing methods with the UVVM VHDL verification framework. Create self-checking testbenches that discover more corner case bugs.

Learn to use guarded blocks to disconnect signal drivers conditionally, and VHDL features like postponed processes and delay modeling mechanisms.

Connect an LED panel to your FPGA design to show messages or images. See how to read pixel data from a file into block RAM using VHDL.

Write testbenches in Python for your VHDL design with the Cocotb hardware verification framework. Learn to use Python’s asynchronous constructs in the Questa and GHDL simulators.

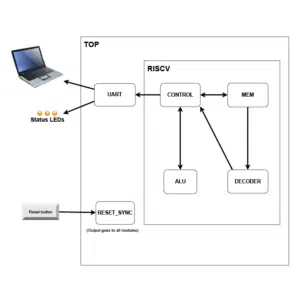

Create a reduced instruction set computer using the RISC-V processor architecture. Learn how a CPU works by implementing one in VHDL and running it on the FPGA.

End of content

End of content