VHDLwhiz Membership

$39This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

Showing 1–12 of 58 results

This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

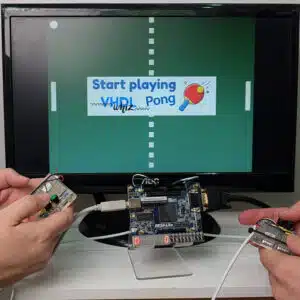

VHDL Pong game implementation course teaching how to control a VGA monitor from an FPGA, including sync signals, gameplay, and displaying images over VGA.

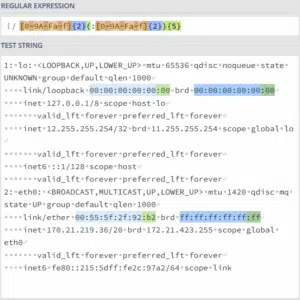

Learn to build a regex processing VHDL module with runtime-reconfigurable pattern matching and Unicode support, using AI-generated Python scripts to create configurations from regexes.

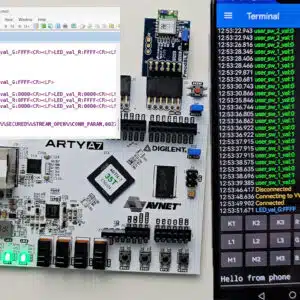

Add Bluetooth connectivity to FPGA projects! Learn to control the color LEDs on your board from a phone and show VHDL signal values in the mobile app.

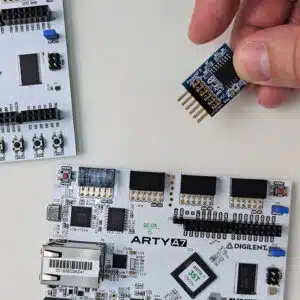

Learn to create a Flash memory controller in VHDL for storing non-volatile data in FPGA projects. This course covers page program (write), read, and erase operations using the quad SPI bus.

Learn to combine VHDL configuration statements with VUnit to maximize testbench utilization and automate test cases for Wishbone bus BFM and RTL DUTs.

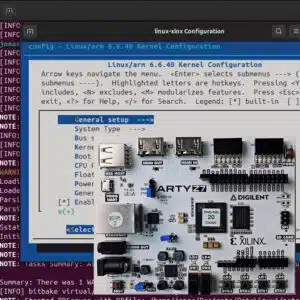

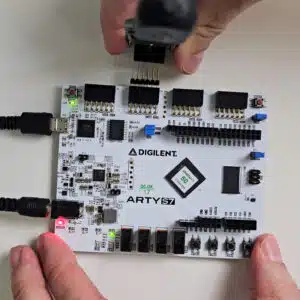

Learn to implement system-on-chip (SoC) designs using embedded Linux for AMD Xilinx FPGAs. This course gives you the skills to succeed with PetaLinux on Zynq-7000 (ARM) devices.

Learn to design and implement high-speed source-synchronous parallel data buses in FPGAs using VHDL.

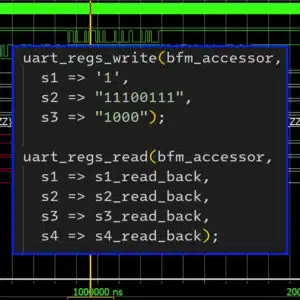

Create a bus functional model (BFM) for a VHDL module with multiple configuration options. Learn to make a system that generates custom BFMs for any interface variant the DUT can have.

Implement the classic Snake game on an FPGA with a 128×32 OLED display. Create a custom GUI to play the game in real-time using the Questa VHDL simulator.

Learn to implement constrained random testing methods with the UVVM VHDL verification framework. Create self-checking testbenches that discover more corner case bugs.

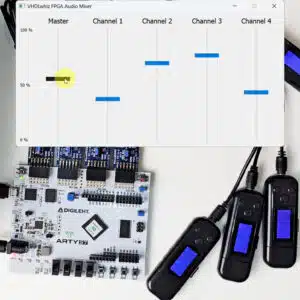

Learn to create a stereo audio mixer using VHDL and multiplier (DSP) primitives in an FPGA and use a Python GUI to control the four input channels.

End of content

End of content