Course: Signal guards and delays in VHDL

Learn to use guarded blocks to disconnect signal drivers conditionally, and VHDL features like postponed processes and delay modeling mechanisms.

Description

Some VHDL features are seldom used. But does that mean they’re not very useful, or is it because people don’t fully understand how they work?

Only you can answer that question after knowing how to use them.

That’s why we are digging into a few of the lesser-used VHDL constructs this month. We’ll find out how to use the following:

- Bus and Register keywords

- Guarded blocks

- Postponed processes

- All about the After keyword

- The Delayed attribute

- And transport delays

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

No FPGA board is required as this course is a pure simulation exercise.

Software used in the course

I am using Windows 11 in the course. All the other software is available for free for Windows and Linux:

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do)

Course outline

The overview below shows the lessons in this course.

1 - Introduction

Some features of VHDL are seldom used. But is that because they are not useful or poorly understood? If it's the latter, we must find out more.

2 - Bus and Register keywords

These are the simplest type of guarded signals that allow you to disconnect driving processes from contributing to their values.

3 - Guarded blocks

With these VHDL constructs, you can conditionally control the activation of signals within a block enclosure.

4 - Postponed processes

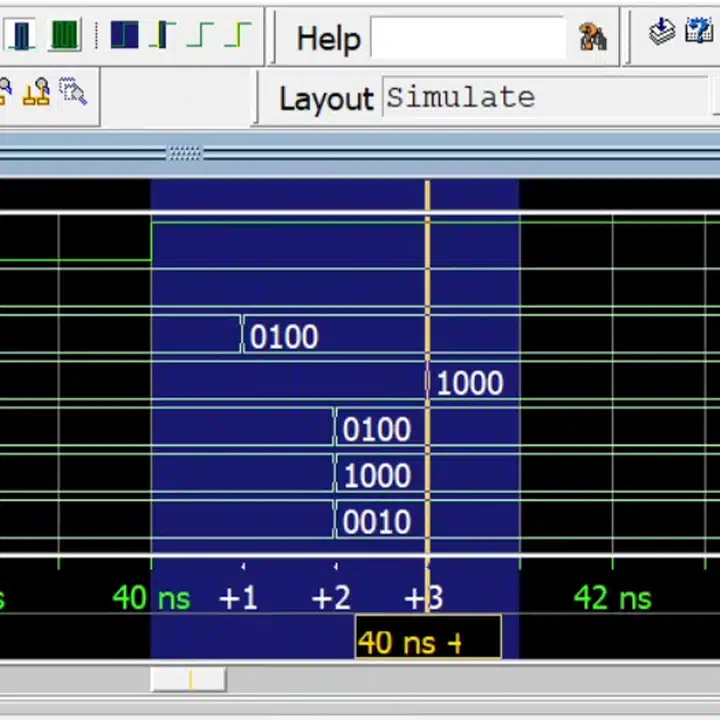

A postponed process is triggered like a normal VHDL process but only runs after all events from non-postponed processes have settled.

5 - After keyword

The After keyword schedules a future value onto a signal. All concurrent signal assignments have an equivalent regular process.

6 - Delayed attribute and Transport keyword

The Delayed attribute and the Transport statement are similar but not identical. Let's see how they differ!

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.