Course: VUnit for structured testbench and advanced BFM design

$59

Learn to create neat testbenches and verification components using this testing framework’s VHDL libraries. Automate your simulation flow with VUnit’s Python test runner.

Description

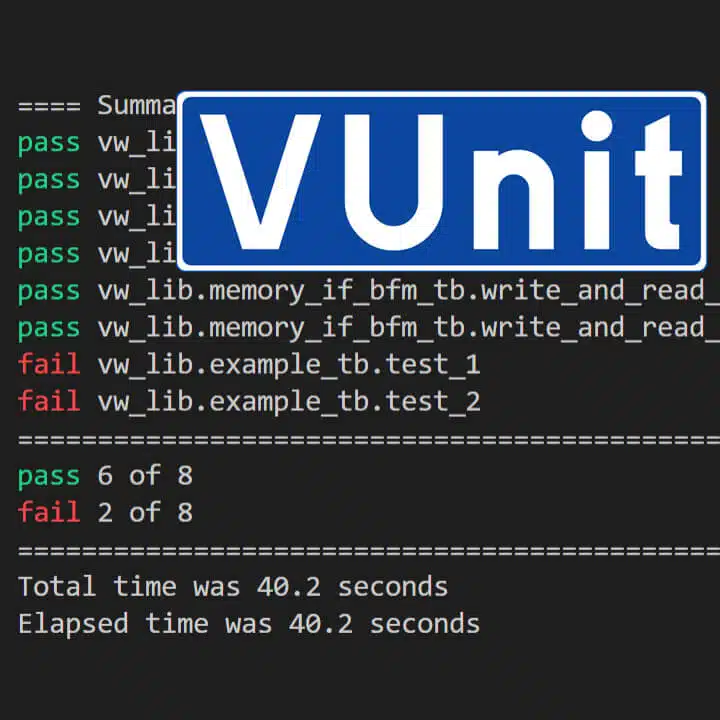

This course explains how to use the VUnit HDL testing framework that combines VHDL and Python to provide unit testing for your FPGA projects.

VUnit is much more than a test runner that automatically compiles and runs your testbenches. It also has an extensive collection of VHDL testing libraries and verification components that you can use to save time and improve the quality of your testbenches.

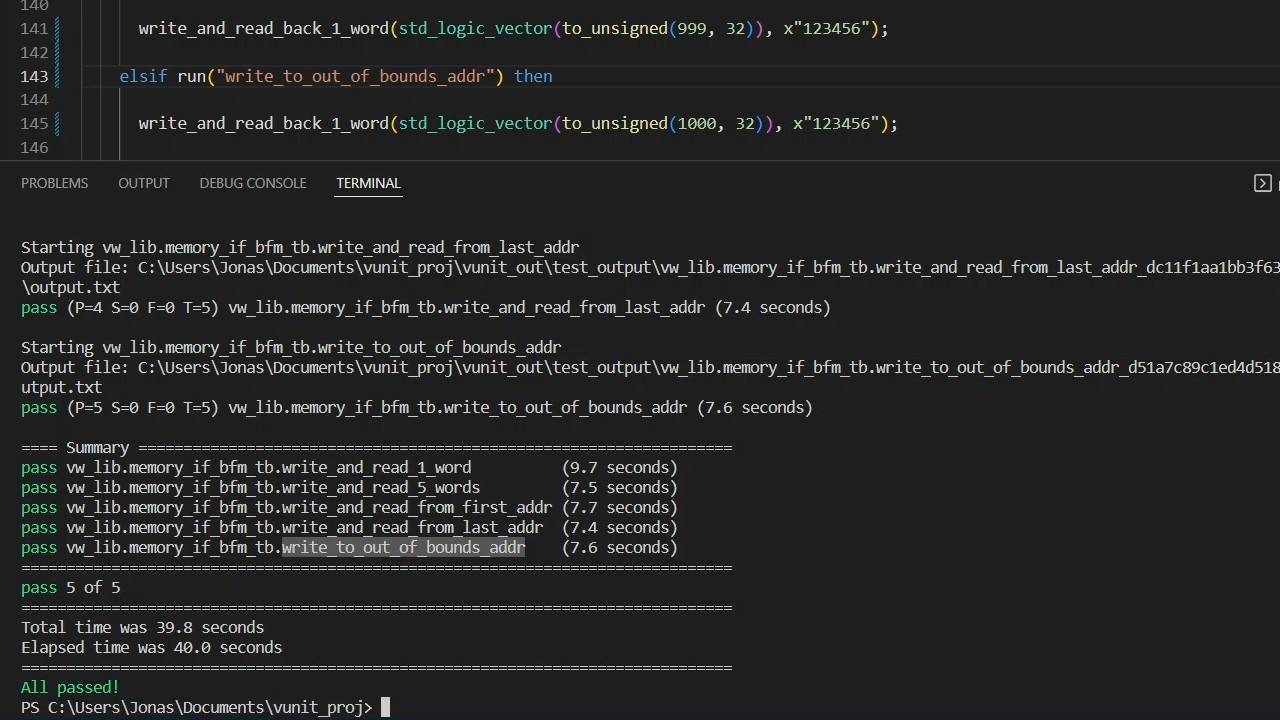

You will learn to use VUnit’s core functionality and how to customize the Python run script to launch regression tests or on-the-fly debugging sessions in the Questa/ModelSim GUI.

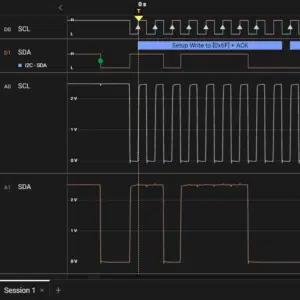

We will also build a bus functional model (BFM) using one of VUnit’s high-level verification components: the Memory Model. And we create a testbench that uses the VUnit VHDL libraries to test the new BFM.

Finally, in the last lesson, we will use VUnit to test something you can’t check with only VHDL. You will learn how to verify functionality that’s supposed to fail in the DUT, like assertion checks in RTL code.

This course is also available in the VHDLwhiz Membership.

The difference is that when you purchase this product, you get permanent access to the course, while the membership charges a monthly fee to access the content.

VHDLwhiz is not affiliated with or endorsed by the VUnit team.

All the lessons are simulation exercises. Thus, you don’t need any FPGA hardware to go through this course.

Software used in the course

I am using Windows 11 in the course. All the other software is available for free for Windows and Linux:

- The VUnit framework

- Python 3

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do) - Git SCM (Optional)

Course outline

The overview below shows the lessons you can access after purchasing this course.

1 - Why VUnit?

VUnit combines VHDL and Python to provide a unit testing framework for your FPGA projects, but that's not all!

2 - Installing VUnit

Get the VUnit framework running on your system quickly and easily.

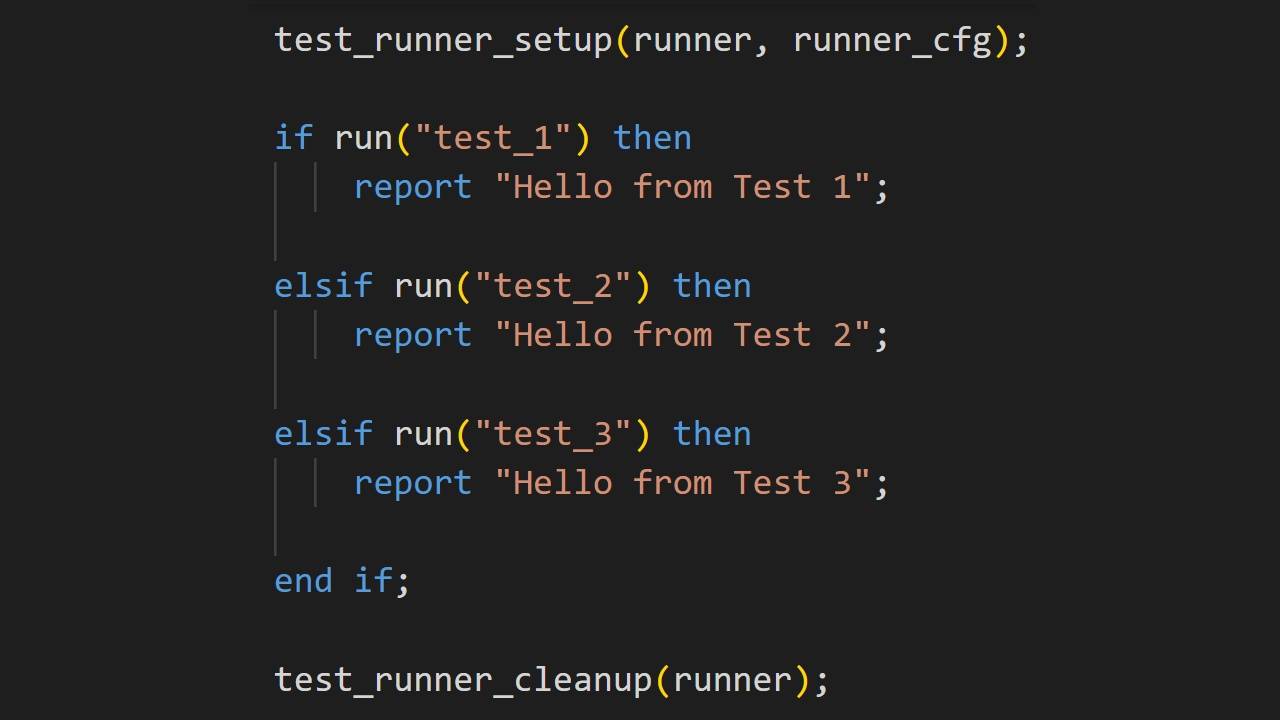

3 - The minimal VUnit testbench

Let's create the first testbench and run it through VUnit!

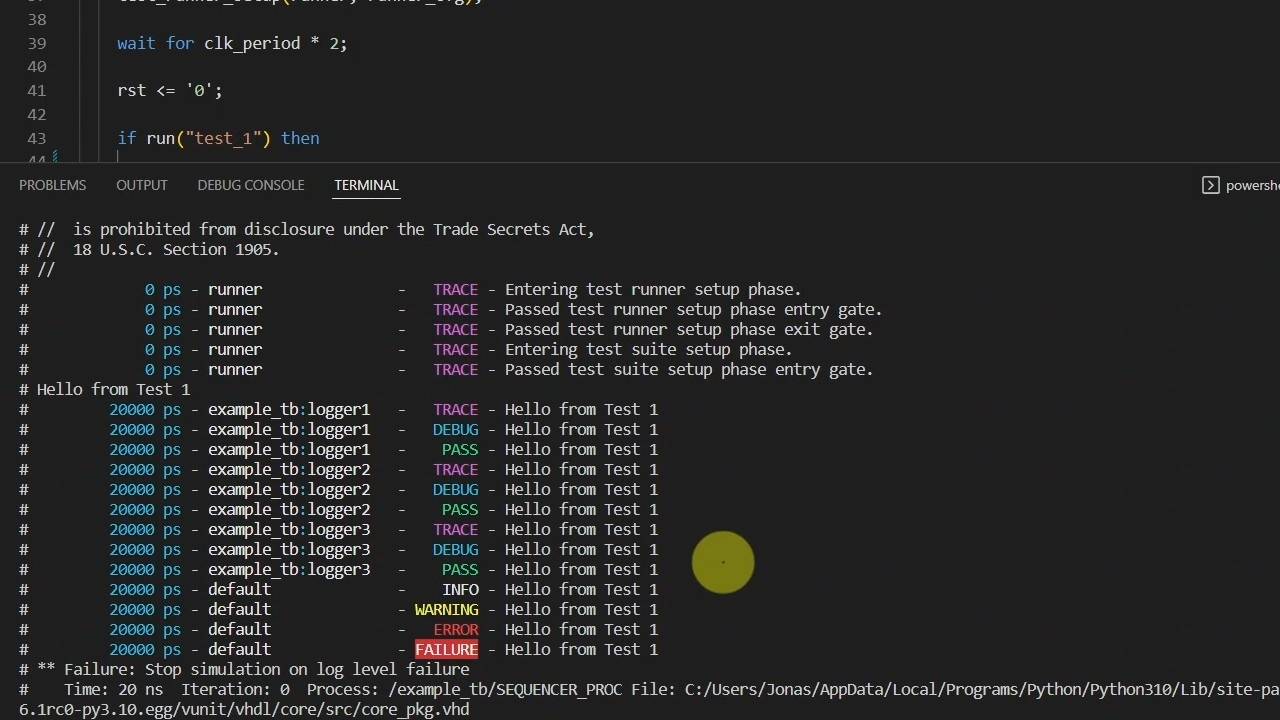

4 - The Logging library

VUnit provides a way to produce nicely formatted printouts from your VHDL testbenches with advanced message filtering options.

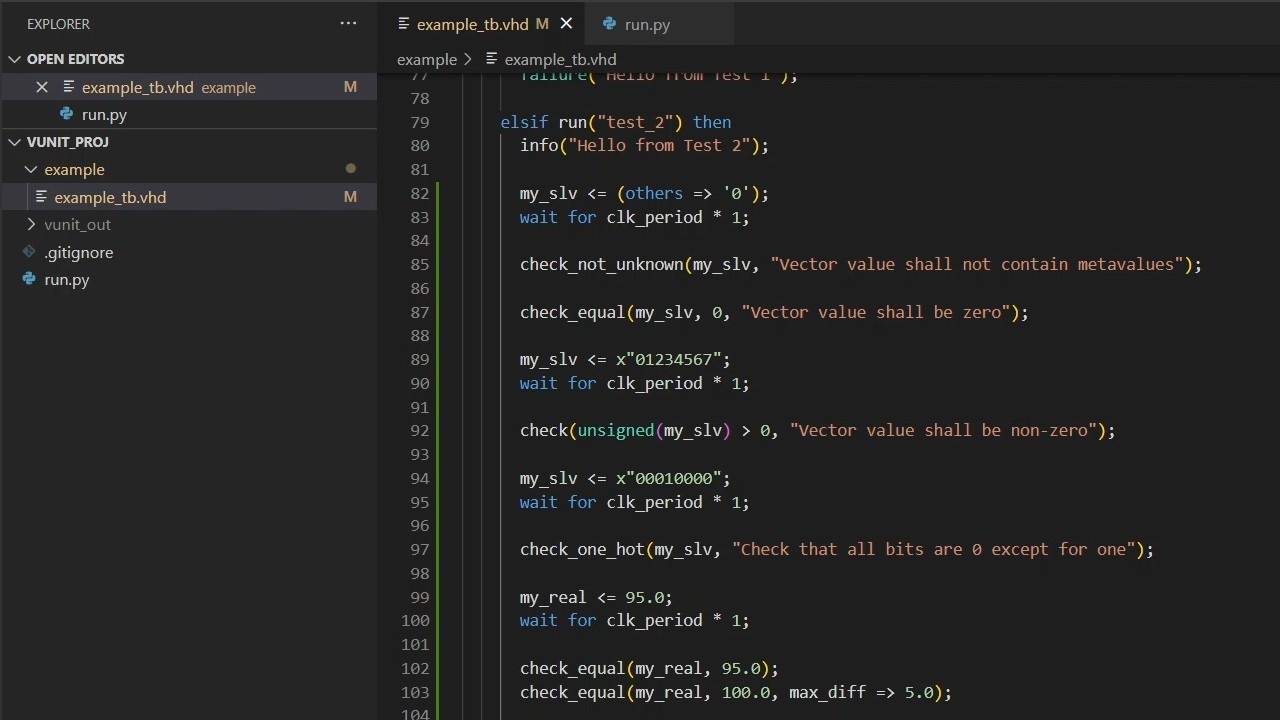

5 - The Check library

VUnit's Check library is a powerful tool for doing assertion-based VHDL verification in a structured manner.

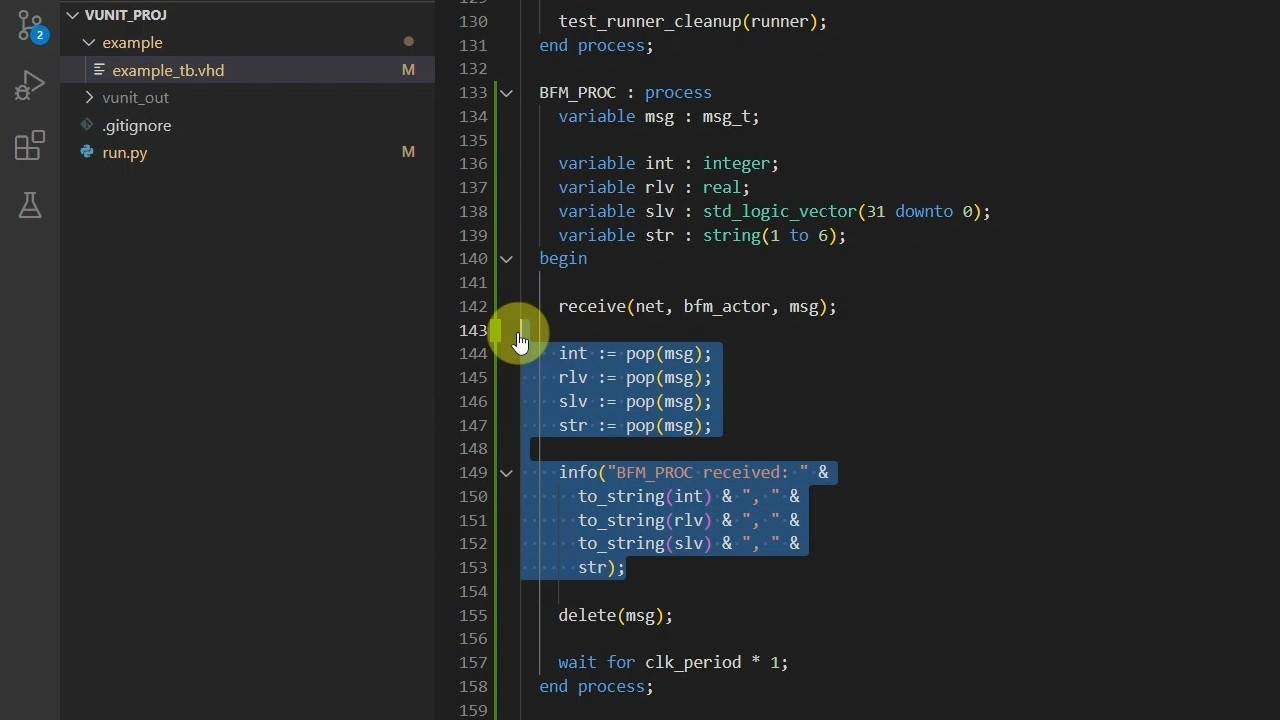

6 - The Communication library: sending a message

This VHDL library provides a messaging system to communicate between processes and verification modules in your testbench.

7 - The Communication library: receiving a reply

Learn how to implement synchronous duplex communication and benefit from custom message types in this lesson.

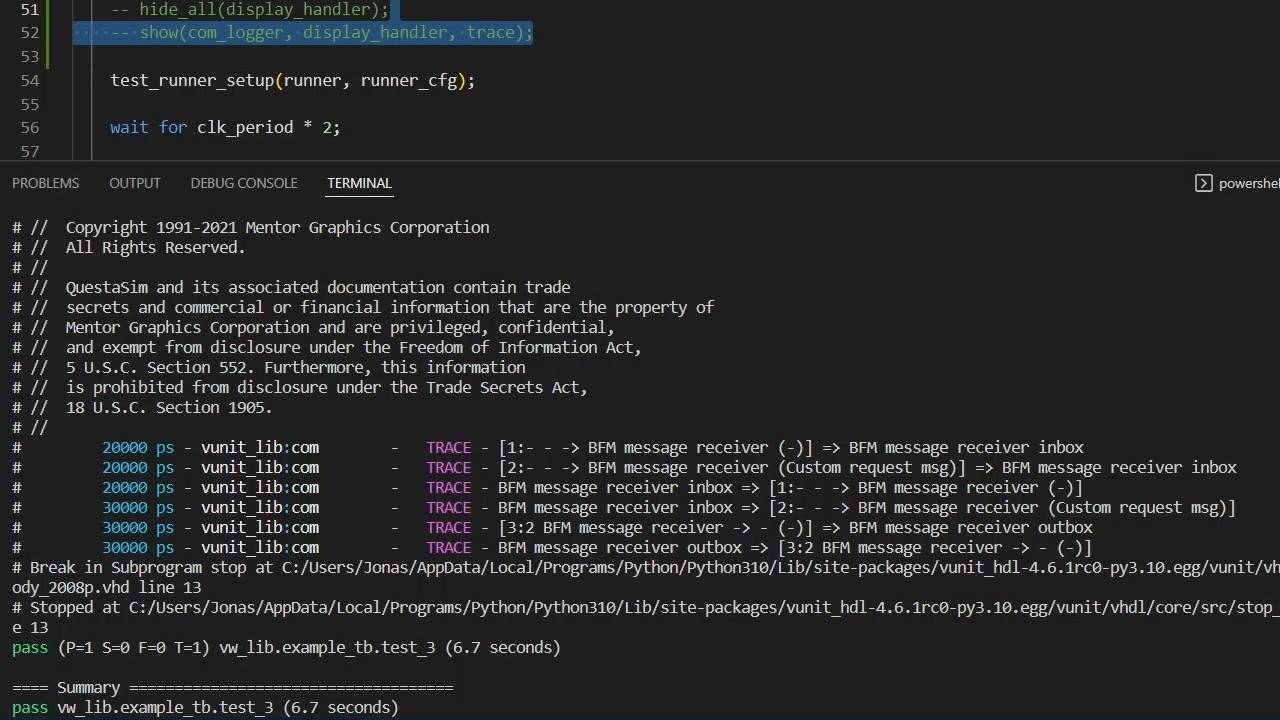

8 - Running the simulator GUI from VUnit and debugging the Python script

VUnit can start the Questa GUI for any test case, and you can alter the run.py script to make the user experience even better.

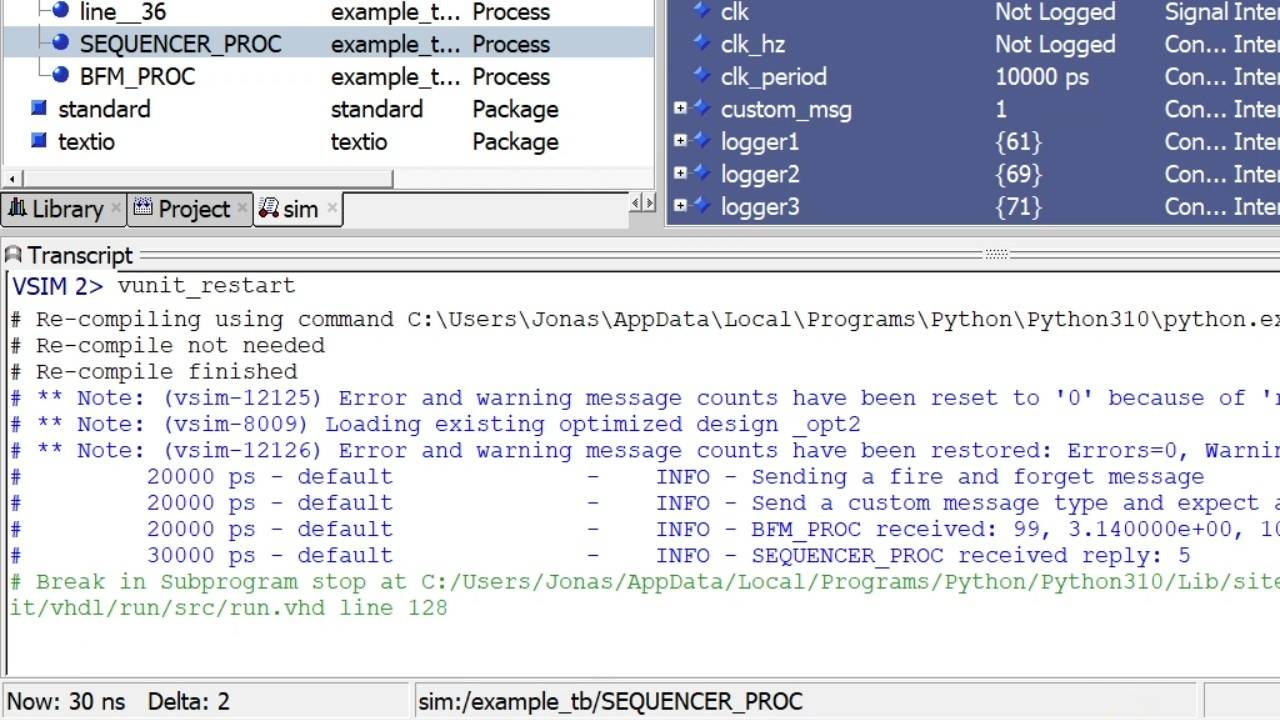

9 - Let's create a new BFM module and testbench using VUnit

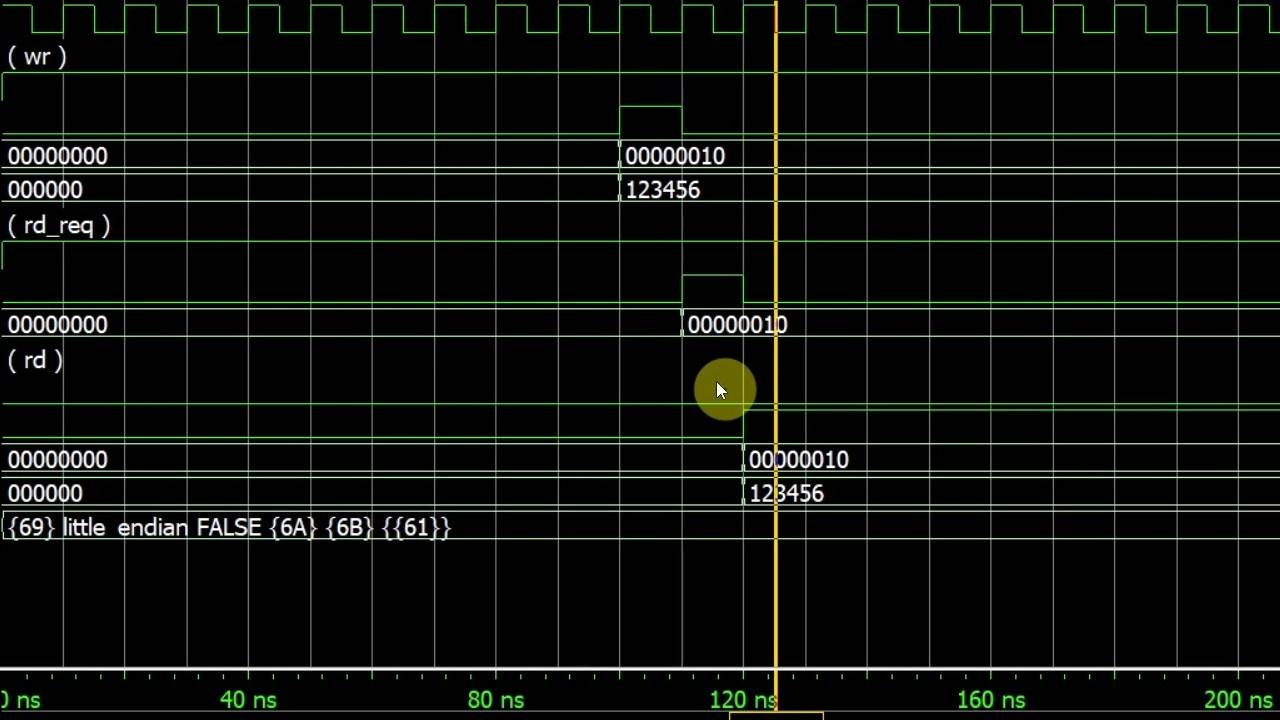

To practice, we will create a bus functional model (BFM ) that uses VUnit's memory model and a testbench that also runs VUnit.

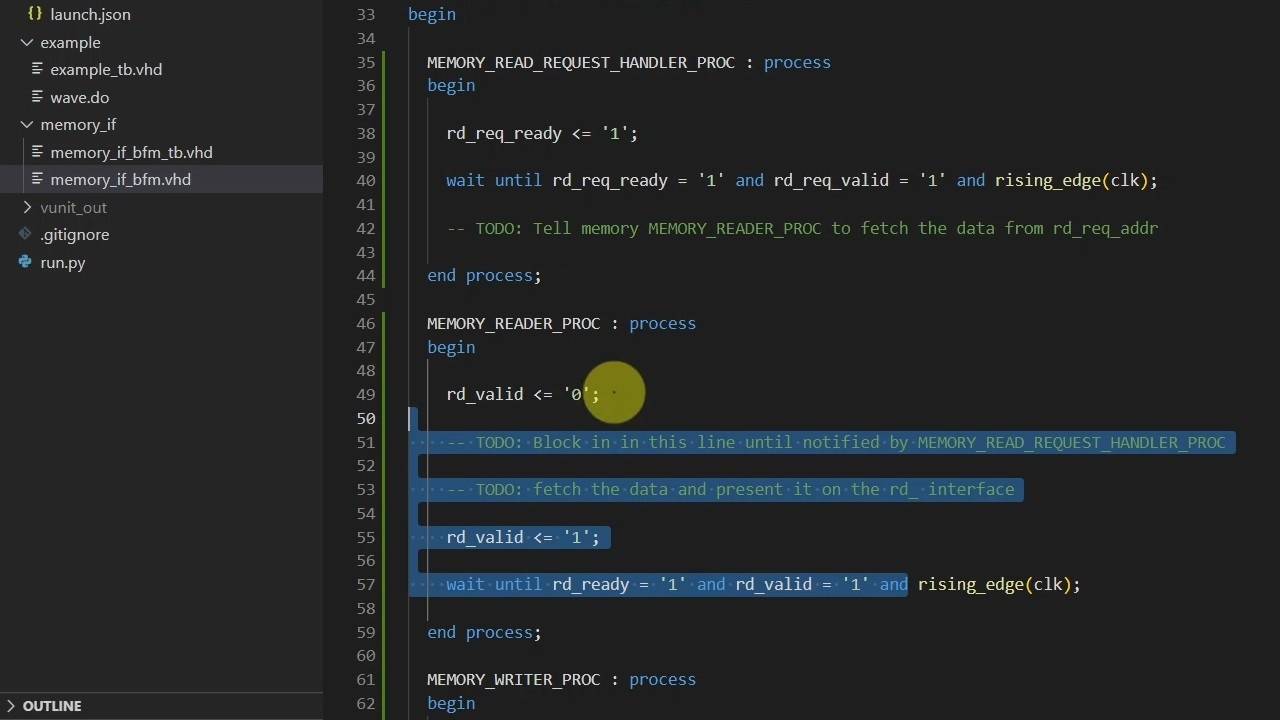

10 - Data stream handler processes

The BFM needs at least three processes to handle the three parallel data streams.

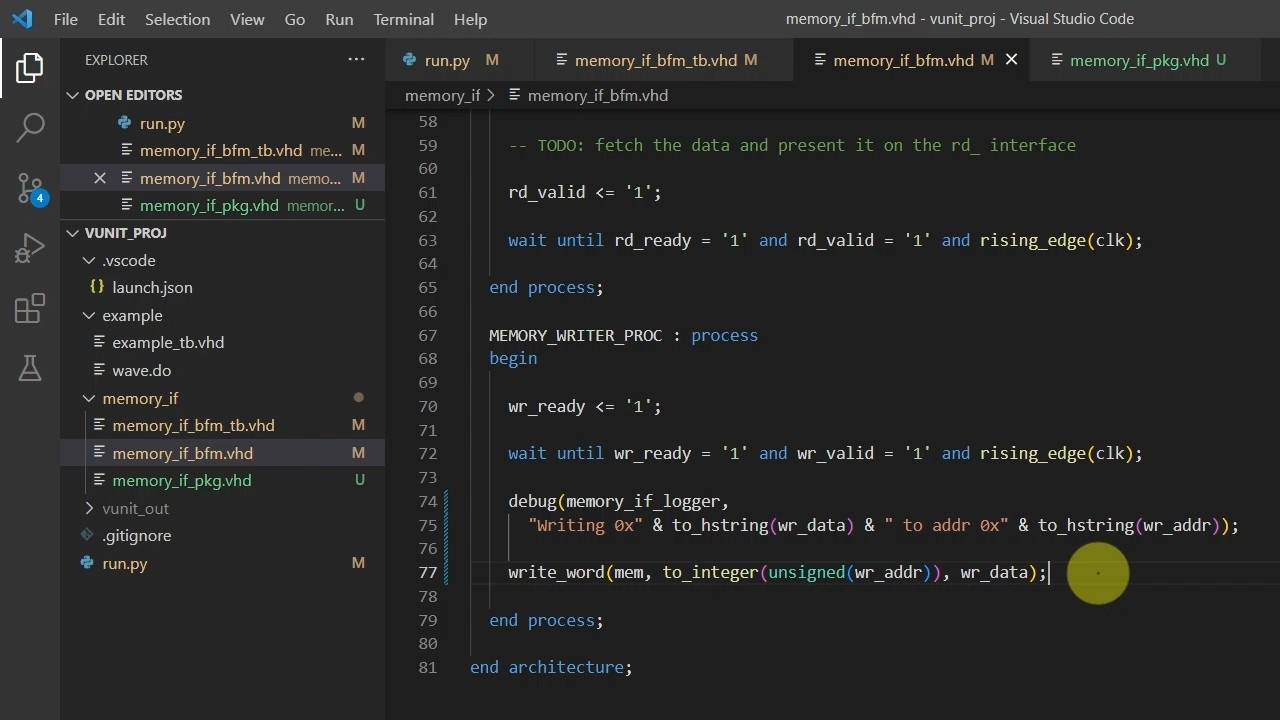

11 - Writing to the memory model and shared BFM package

A good way to provide access to the BFM's functionality is to create a shared package that the BFM and the testbench can import.

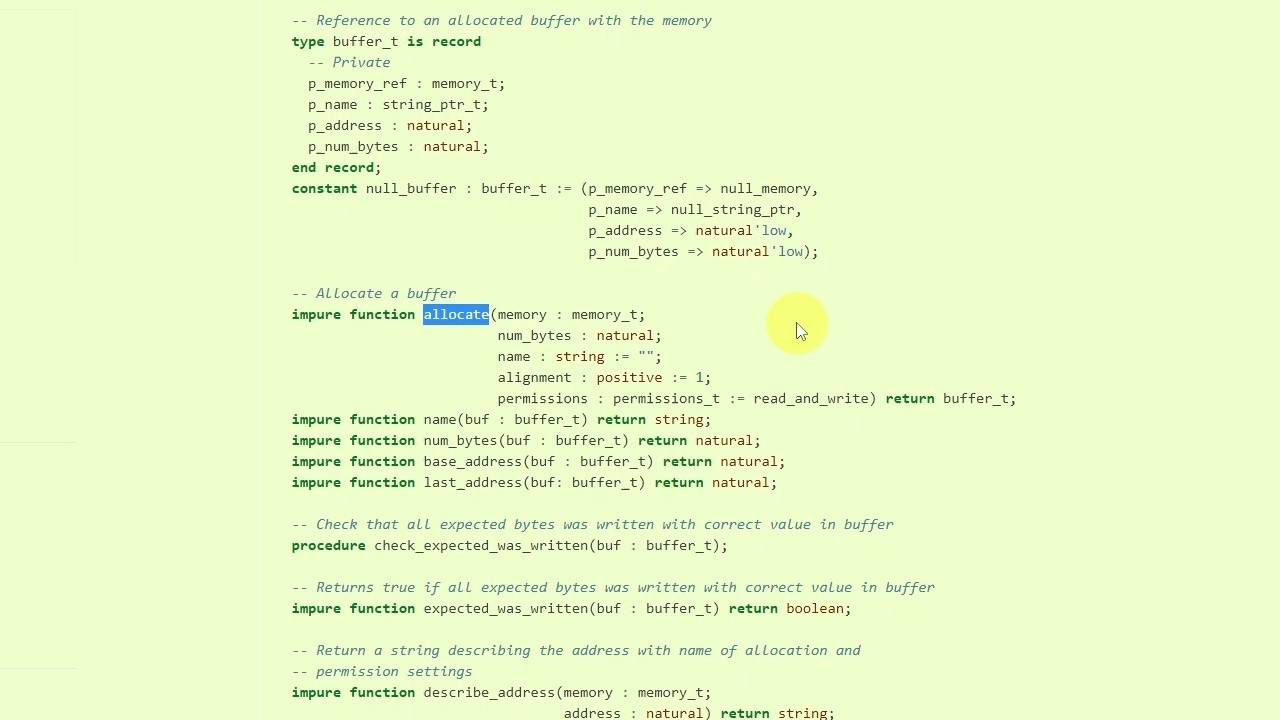

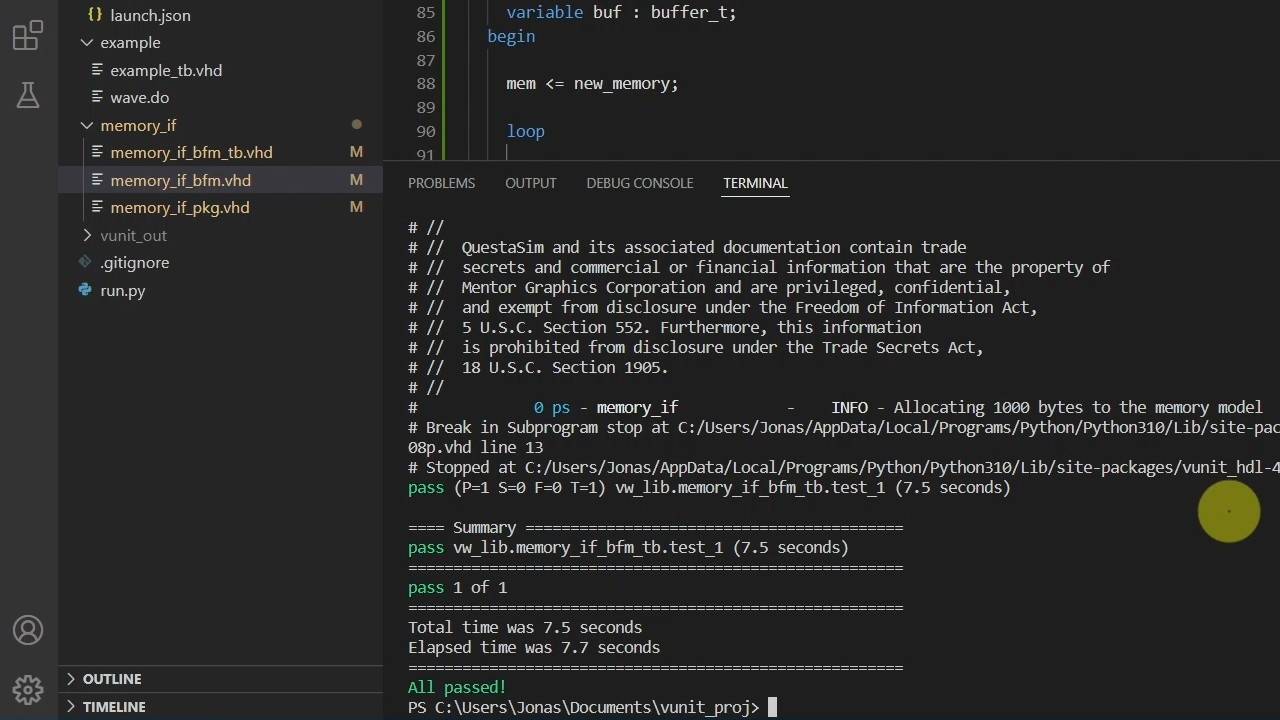

12 - Allocating memory and the command executor

We must initialize the memory model and allocate sufficient memory at run-time before we can write to or read from it.

13 - Request read and reading from the memory model

We will use VUnit's Communication library to queue read requests in the BFM and notify that reader process.

14 - Adding more test cases

Let's extend the testbench to do back-to-back reads and test out-of-bounds addresses.

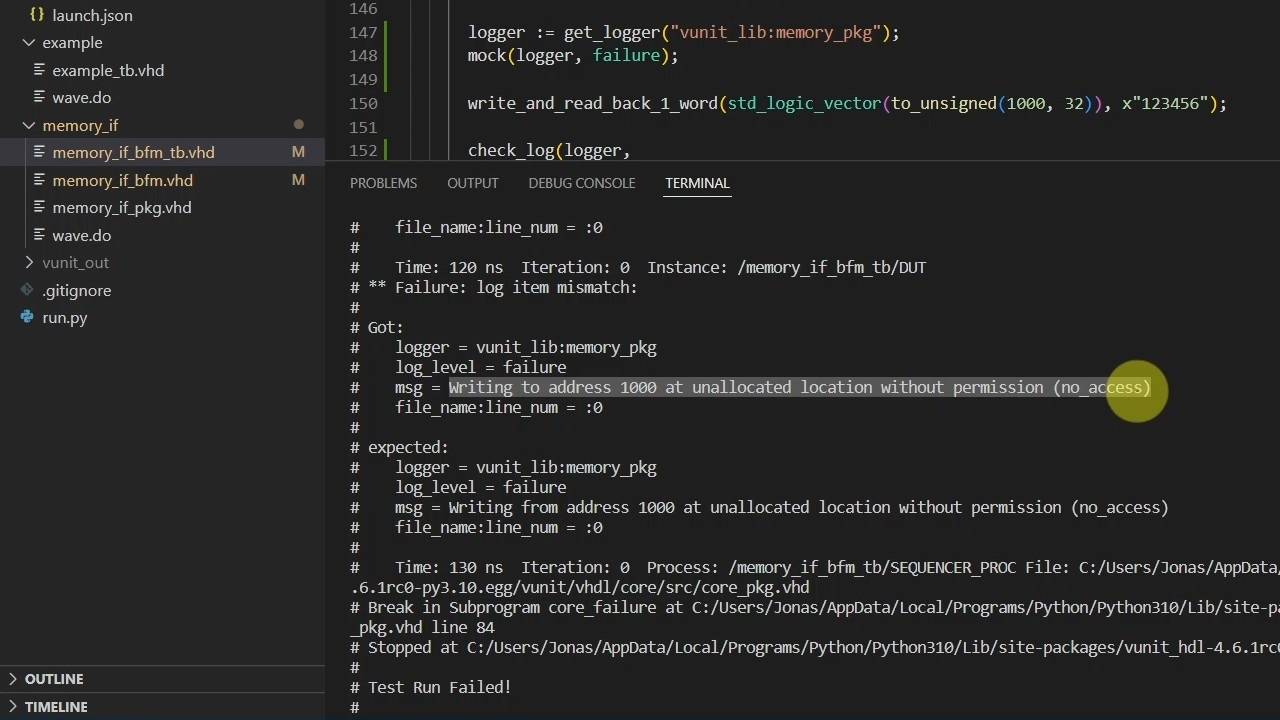

15 - Mocking to verify test cases that are supposed to fail

Mocking is a clever feature from VUnit's Logging library that allows you to test that assertion checks in the DUT fail when they are supposed to.

Reviews

There are no reviews yet.