Course: VHDL audio mixer using FPGA DSP blocks

Learn to create a stereo audio mixer using VHDL and multiplier (DSP) primitives in an FPGA and use a Python GUI to control the four input channels.

Description

This course teaches how to create a 4-input stereo sound mixer using VHDL and multipliers in a Xilinx FPGA using Vivado and VHDL.

We’ll also use artificial intelligence (AI) to make a neat GUI in Python to control the gain factors in our hardware mixer in real time.

Here are some things this course teaches you:

- How to implement an audio-processing circuit using VHDL and hardware multipliers

- Creating a derived clock with a mixed-mode clock manager (MMCM)

- Adding Verilog modules to your VHDL design

- Normalizing audio

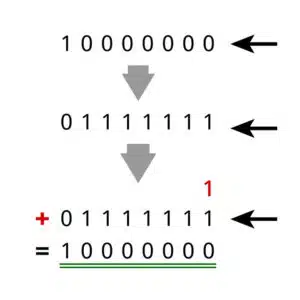

- Dealing with overflow

- Making a self-checking testbench in Vivado

See the video below to learn more about this course.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

I’m using the Digilent Arty S7-50 board with a Spartan-7 FPGA, but you can use any other Xilinx board. Modifying the constraint file to fit a different pinout is easy.

Doing the course as a simulation exercise is also fine, as I’ll show everything on my setup anyway.

Hardware used in the course

- Arty S7-50: Xilinx Spartan-7 FPGA (SKU: 410-352)

Resellers: Digilent, Farnell, Newark, Mouser, DigiKey, RS Electronics

(You can modify the design to use a different FPGA board) - Digilent Pmod I2S2 Audio Input and Output module (SKU: 410-379)

Resellers: Digilent, Mouser, DigiKey, RS Electronics - A generic speaker with a built-in amplifier and mini-jack input

- Five mini jack male-to-male audio cables

- Four MP3 players with SD cards

(Or any other audio sources)

Software used in the course

I am using Windows 11 in the course. All the other software is available for free for Windows and Linux:

- Xilinx Vivado

- Microsoft Visual Studio Code

(Any editor will do) - A Python interpreter

And the PyQt5 library (install it easily through Pip)

Course outline

The overview below shows the lessons in this course.

1 - Introduction

Here's what we will create and what you will learn from this course

2 - The hardware used in the course

I'm using the Arty S7 FPGA board and four Pmod I2S2 analog/digital audio converter modules from Digilent. But you may use a different setup or no hardware at all to complete this course.

3 - Demo project

We'll base our design on Digilent's Pmod I2S2 demo project. Let's begin by testing it on the FPGA board!

4 - New project setup

Let's create a new Vivado project, generate an MMCM IP core using the clocking wizard, and import the Verilog I2S interface module.

5 - Top VHDL module with audio pass-through

We'll instantiate the Verilog I2S interface module in the new VHDL top and check that we can play music through it.

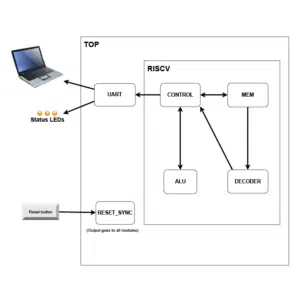

6 - Audio gain control using UART-accessible registers

VHDLwhiz's test interface generator tool can create a VHDL module with custom output registers and a Python script to access them.

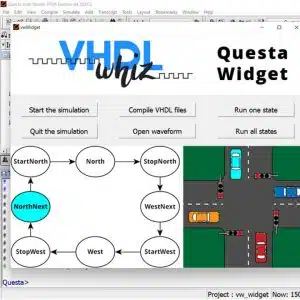

7 - Audio mixer GUI

Here's the GUI (graphical user interface) we'll use as a front-end for our FPGA-based audio mixer

8 - Instantiating a multiplier in the VHDL code

Multiplier or DSP (digital signal processing) slices in FPGAs are specialized primitives that are very efficient at multiplying numbers. We'll use one to control the audio gain.

9 - All channels mixed

After duplicating the gain control circuit for the other inputs and the master volume, we'll sum all channels using adders to create the mixed audio output.

10 - Dealing with overflow

To mitigate distortion caused by overflow, we'll cap the mixed audio signal to within the minimum and maximum bounds of a 24-bit signed integer.

11 - Top testbench

Let's review the self-checking testbench for the top-level VHDL module and the BFMs (bus functional models) for the ADC and DAC chips.

12 - Vivado workaround

We have to make some adaptions to the testbench and run it through a Tcl script to get around the Vivado simulator's patchy VHDL-2008 support. But it works!

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.