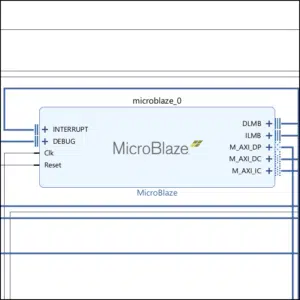

Course: MicroBlaze SoC design

$59Learn how to build a system-on-chip (SoC) design by using a MicroBlaze soft-core processor, existing IP cores, and custom VHDL modules.

This content from the VHDLwhiz shop is suitable for advanced users.

Showing 13–20 of 20 results

Learn how to build a system-on-chip (SoC) design by using a MicroBlaze soft-core processor, existing IP cores, and custom VHDL modules.

Learn to implement the I²S protocol in VHDL and configure the ADAU1761 ADC/DAC audio codec chip on the Xilinx Zedboard with bare-metal C programming.

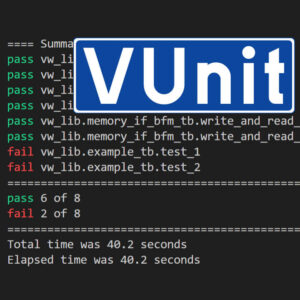

You don’t have to use only one VHDL verification framework. We can pick and choose the features we need and combine them to create awesome testbenches.

Learn to create neat testbenches and verification components using this testing framework’s VHDL libraries. Automate your simulation flow with VUnit’s Python test runner.

The Universal VHDL Verification Methodology (UVVM) framework provides a utility library, reusable verification components, and a way to structure your VHDL testbenches.

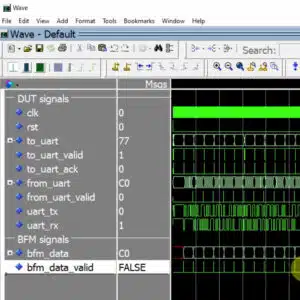

Build a testbench that separates bit-level logic into separate modules and uses a command interface to control executor processes.

Learn to achieve functional coverage in VHDL testbenches with pseudo-random DUT interactions by using the OSVVM VHDL framework.

Learn to develop high-speed image processing systems using VHDL. See how to simulate pixel filters using JPG pictures in a VHDL testbench.

End of content

End of content