VHDL registers UART test interface generator

$39

This tool generates a VHDL module and a Python script to read from or write to any number of custom FPGA registers using UART.

Description

With this tool, you can effortlessly implement test interfaces for your VHDL projects. It generates matching VHDL modules, instantiation templates, and accessor scripts to write or read the register values over UART or print them in a neat table.

Watch the video above for a live demo of what the interface generator can do!

The script generates a VHDL module with UART connectivity and input/output registers of any number, bit width, and combination. The UART accessible VHDL signals may be of type std_logic, std_logic_vector, signed, or unsigned.

Here’s a demo run of the tool to generate an interface for the Digilent Arty-S7 board’s peripherals and four internal registers:

PS C:\demo\uart_regs-1.0.0> python gen_uart_regs.py `

>> btn=4 sw=4:in:signed led=4:out:unsigned led0_r=1:out `

>> led0_g=1:out led0_b=1:out reg0=10:out reg1=16:out `

>> reg2=32:out:unsigned reg3=40:out:unsigned

Collected register information:

Register Name Bit Length Type Mode

=========================================================

btn 4 std_logic_vector in

sw 4 signed in

led 4 unsigned out

led0_r 1 std_logic out

led0_g 1 std_logic out

led0_b 1 std_logic out

reg0 10 std_logic_vector out

reg1 16 std_logic_vector out

reg2 32 unsigned out

reg3 40 unsigned out

Generating files:

generated/uart_regs.vhd

generated/uart_regs.py

generated/instantiation_template.vho

This will produce a custom VHDL module, instantiation template, and Python script for conveniently reading or writing the registers from the command line.

Here’s the entity generated by the example command shown above:

entity uart_regs is

generic (

clk_hz : positive;

baud_rate : positive := 115200

);

port (

clk : in std_logic;

rst : in std_logic;

uart_rx : in std_logic;

uart_tx : out std_logic;

-- UART accessible registers

btn : in std_logic_vector(3 downto 0);

sw : in signed(3 downto 0);

led : out unsigned(3 downto 0);

led0_r : out std_logic;

led0_g : out std_logic;

led0_b : out std_logic;

reg0 : out std_logic_vector(9 downto 0);

reg1 : out std_logic_vector(15 downto 0);

reg2 : out unsigned(31 downto 0);

reg3 : out unsigned(39 downto 0)

);

end uart_regs;

When creating a new interface, the tool produces a VHDL module and matching Python script for accessing the registers.

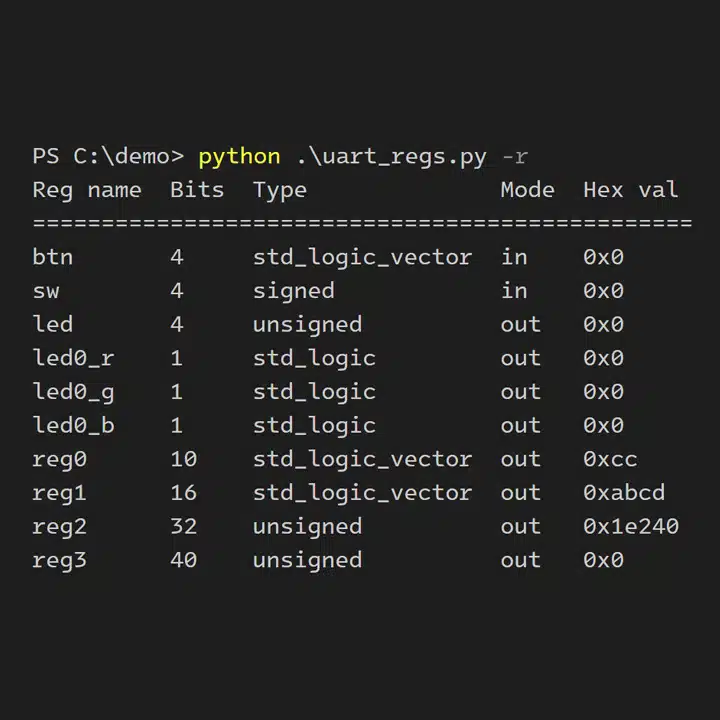

The uart_regs.py script knows the composition of the registers in the uart_regs.vhd module, and you can use it to easily read all registers and write to the out mode registers.

You can use the script from the command line in Windows or Linux, or you can incorporate it in other Python scripts. The uart_regs.py file contains a UartRegs class, which you can make objects from to create custom test interface scripts.

This listing shows a write followed by a read of the example interface we created earlier:

C:\demo\xilinx_arty_s7_50>python uart_regs.py -w reg3=123456789 Write succeeded C:\demo\xilinx_arty_s7_50>python uart_regs.py -r Reg name Bits Type Mode Hex val Int val ============================================================== btn 4 std_logic_vector in 0x0 sw 4 signed in 0xf -1 led 4 unsigned out 0x5 5 led0_r 1 std_logic out 0x1 led0_g 1 std_logic out 0x1 led0_b 1 std_logic out 0x1 reg0 10 std_logic_vector out 0x0 reg1 16 std_logic_vector out 0x0 reg2 32 unsigned out 0x0 0 reg3 40 unsigned out 0x75bcd15 123456789

👇 Refer to the user manual for more information about using this tool.

VHDL registers UART test interface generator – User manual.pdf

After purchasing this product, you get access to a detailed video walkthrough about using the tool.

This project is also available in the VHDLwhiz Membership.

The difference is that when you purchase this product, you get immediate access to the downloadable Zip file, while the membership charges a monthly fee to access the content.

License agreement

MIT License

Copyright (c) 2026 Jonas Julian Jensen

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Reviews

There are no reviews yet.