Course: Delta cycles in-depth

Understanding how delta cycles work in VHDL is key to becoming proficient in FPGA design. This course teaches you how signal scheduling works in simulation.

Description

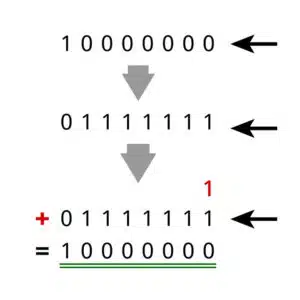

Delta cycles are zero-time timesteps used by simulators. For the novice VHDL developer, the concept can seem difficult to grasp. But as we shall see, there is nothing mystical or magical about delta cycles.

This course teaches everything you need to know about how signal signal scheduling works in simulation. I’ll show you how to view delta cycles in the waveform and how you can use them to your advantage in testbenches.

Do delta cycles exist in the FPGA, and what happens to them after synthesis?

Let’s find out together!

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Hardware used in the course

You don’t need the board, as I’m just using it in the final lesson to demonstrate a simulation mismatch due to misunderstanding how delta cycles work.

Software used in the course

I am using Windows in the course. All the other software is available for free for Windows and Linux:

⚠ Notice: free educational license required

Lattice Semiconductor now charges over $350/year for the iCEcube2 software.

Fortunately, VHDLwhiz, in cooperation with Lattice, offers a 1-year educational license for iCEcube2 to customers who purchase a course that uses the iCE40 FPGA.

Reply to the purchase confirmation email to request a free license.

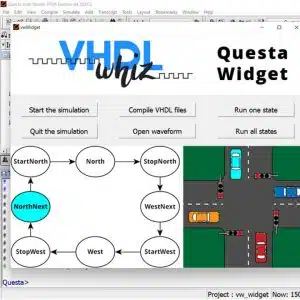

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do) - Lattice iCEcube2 Design Software

Course outline

The overview below shows the lessons in this course.

1 - Why you need to understand this

Delta cycles play a crucial role in how signal scheduling and inter-process communication works in VHDL.

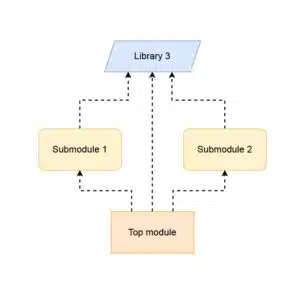

2 - Signal scheduling in VHDL

You can learn how every simulator executes your VHDL code by drawing the signaling scheduling table on paper.

3 - Future values

Delta cycles are only necessary for modeling events that are 0 ns into the future.

4 - Creating delta cycles deliberately

5 - Used for testbench interfaces

We can use delta cycles to build testbench interfaces that don't consume real-time.

6 - Delta cycles after synthesis

Delta cycles play a role synthesis of VHDL code, but no all delta cycles translate into hardware.

7 - Simulation mismatch due to delta delays

You need to be aware of these pitfalls with delta cycles that can cause a mismatch between the simulation and implementation.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.