VHDL module: AXI-style UART

$15

This project contains three general-purpose, AXI compatible, universal asynchronous receiver-transmitter (UART) modules.

Description

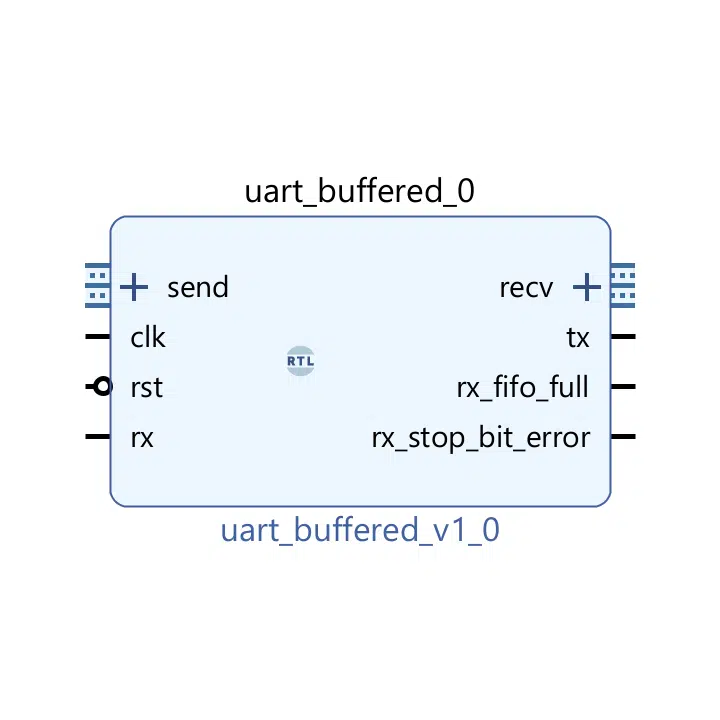

All three modules have built-in flow control through the use of ready/valid handshake signals. And because the signal naming scheme matches the Xilinx AXI standard, the send and recv ports will appear as bus interfaces in the Vivado Block Design editor.

You can also use the modules standalone in RTL code. You don’t need to utilize the ready or valid signals if you feel confident that there will be no overflow or if you don’t care about lost bytes.

The system clock frequency and the baud rate are configurable. Data bit count is fixed to 8 (one byte), stop bits is set to 1, and parity is not used.

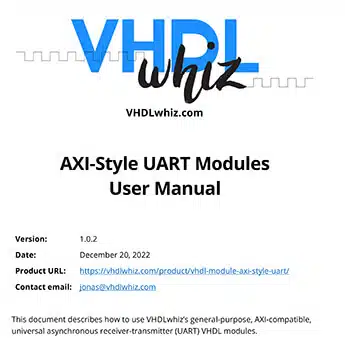

Click here to download the UART – User Manual:

The Zip file contains demo projects for the following development boards:

- Lattice iCEstick (iCEcube2)

- Xilinx Arty A7 35T (Vivado)

- Xilinx Arty S7 50 (Vivado)

- Terasic DE10-Lite (Quartus) + Digilent Pmod USBUART *

* Because the DE10-Lite board doesn’t have a built-in UART to USB interface, we will use Digilent’s pluggable USBUART Pmod module for that.

This project is also available in the VHDLwhiz Membership.

The difference is that when you purchase this product, you get immediate access to the downloadable Zip file, while the membership charges a monthly fee to access the content.

UART RX/TX with block RAM buffering

The uart_buffered.vhd module has build-in flow control through the AXI-style read/valid signaling scheme on the send and receive ports. Data transfer only happens when <send/recv>_tvalid and <send/recv>_tready are '1' during the same rising clock edge.

Buffered bytes are stored in block RAM until they are sent by this module or read from it. The block RAM depth is configurable through generics, but the FIFO size will be that number minus one because the internal FIFO always keeps one slot open to distinguish between the full and empty states.

The listing below shows the entity for this module.

entity uart_buffered is

generic (

clk_hz : positive;

baud_rate : positive;

rx_fifo_ram_depth : positive := 2048;

tx_fifo_ram_depth : positive := 2048

);

port (

clk : in std_logic;

rst : in std_logic;

-- UART input/output lines

rx : in std_logic;

tx : out std_logic;

-- Received byte (sample on pulsed valid)

recv_tdata : out std_logic_vector(7 downto 0);

recv_tvalid : out std_logic;

recv_tready : in std_logic;

-- Word to send (ready/valid handshake)

send_tdata : in std_logic_vector(7 downto 0);

send_tvalid : in std_logic;

send_tready : out std_logic;

-- Error conditions ('0' = no error)

rx_fifo_full : out std_logic;

rx_stop_bit_error : out std_logic

);

end uart_buffered;

UART RX

The uart_rx.vhd module contains an unbuffered UART receiver. Received data appears on the recv_tdata line and is valid when recv_tvalid is '1'.

The listing below shows the entity for the receiver module.

entity uart_rx is

generic (

clk_hz : positive;

baud_rate : positive

);

port (

clk : in std_logic;

rst : in std_logic;

-- UART input line

rx : in std_logic;

-- Received byte (sample on pulsed valid)

recv_tdata : out std_logic_vector(7 downto 0);

recv_tvalid : out std_logic;

-- Is '1' if the stop bit of the latest byte was '0'

stop_bit_error : out std_logic

);

end uart_rx;

UART TX

The uart_tx.vhd module contains an unbuffered UART transmitter. Data put on send_tdata is transmitted when send_tvalid is '1'.

The listing below shows the entity for the transmitter module.

entity uart_tx is

generic (

clk_hz : positive;

baud_rate : positive

);

port (

clk : in std_logic;

rst : in std_logic;

-- UART output line

tx : out std_logic;

-- Word to send (ready/valid handshake)

send_tdata : in std_logic_vector(7 downto 0);

send_tvalid : in std_logic;

send_tready : out std_logic

);

end uart_tx;

License agreement

MIT License

Copyright (c) 2026 Jonas Julian Jensen

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Reviews

There are no reviews yet.