Course: Functional coverage-driven VHDL testbench using UVVM

Learn to implement constrained random testing methods with the UVVM VHDL verification framework. Create self-checking testbenches that discover more corner case bugs.

Description

This course teaches how to create self-checking VHDL testbenches that use advanced randomized testing strategies to verify VHDL designs.

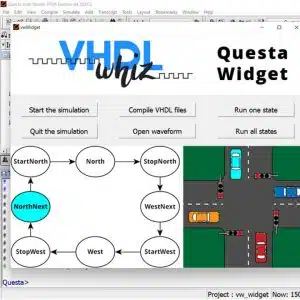

We use the free and open-source Universal VHDL Verification Methodology (UVVM) framework and a free version of the Questa simulator to check a device under test (DUT) from the VHDLwhiz library.

Constrained random verification (CRV) is a method that relies on letting the testbench randomly interact with the device under test. Then, based on specific constraints or limits, the testbench decides which stimuli to use and when to stop.

In this course, we implement a CRV-based testbench using UVVM features like bus functional models (BFMs /VVCs), intelligent randomization, scoreboards, and logging and checking functions.

You will learn to set up coverage points to monitor the DUT during simulation and sample hits in “bins” to ensure 100% functional coverage of events you want to test in your VHDL code.

See the video below for a preview of selected lessons. (The previews start at 3:10)

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

No FPGA board is required as this course is a pure simulation exercise.

Software used in the course

I am using Windows 11 in the course. All the other software is available for free for Windows and Linux:

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do) - The Universal VHDL Verification Methodology (UVVM) framework

Course outline

The overview below shows the lessons in this course.

1 - Introduction

Welcome to the course! Here's what we will do.

2 - Download and compile UVVM

Let's start by downloading the UVVM framework, customizing it, and compiling it for use in Questa/ModelSim.

3 - Device under test (DUT)

Here's the VHDL module that will be the target of our UVVM testbench. Let me show you how it works!

4 - Setting up the UVVM testbench

To maintain order in this complex project, we'll organize the verification code into packages, a context file, and a test harness module in addition to the main testbench VHDL file.

5 - Encode and decode functions

We must write functions to interpret the DUT's data framing protocol. We also need a custom data type to represent encoded and unencoded words.

6 - Using VHDL verification components (VVCs)

Let's use verification components from the UVVM framework to generate the clock and for UART communication with the DUT.

7 - Procedure for sending encoded words over UART

Let's take a look at code coverage in Questa and create a subprogram to send out_regs values to the DUT using the custom data framing protocol.

8 - Procedure for checking DUT out_regs values

We need a VHDL procedure to programmatically check that the DUT's out_regs outputs reflect the values we sent over UART.

9 - Procedure for setting DUT in_regs values

The uart_regs_backend module will sample all input and output registers when we send a read command. Let's create procedures for testing that.

10 - Procedure for receiving and checking UART data

We need a way to receive and check UART data sent from the DUT to the testbench. Let's create a procedure for that!

11 - Generating random byte values

We'll use UVVM's Optimized Randomization methods to generate new byte values to send over UART to the DUT without repeatedly selecting the same values.

12 - Functional coverage bins for sent byte data

Let's turn this into a functional coverage-driven randomized testbench by using UVVM's protected type t_coverpoint to sample tested byte values.

13 - FSM analysis

To measure the functional coverage of the two finite-state machines (FSMs) in the DUT, we need to examine the code to identify possible state changes.

14 - State transition coverage collector

We'll create a new VHDL module to sample functional coverage data for the DUT's FSMs, including state hits and state changes.

15 - Error injection and corner case bug discovery

Let's insert random control characters in the UART data to achieve 100% functional coverage of the FSM. We may discover obscure bugs if we are lucky. 😉

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.