VHDL module: Wishbone crossbar interconnect

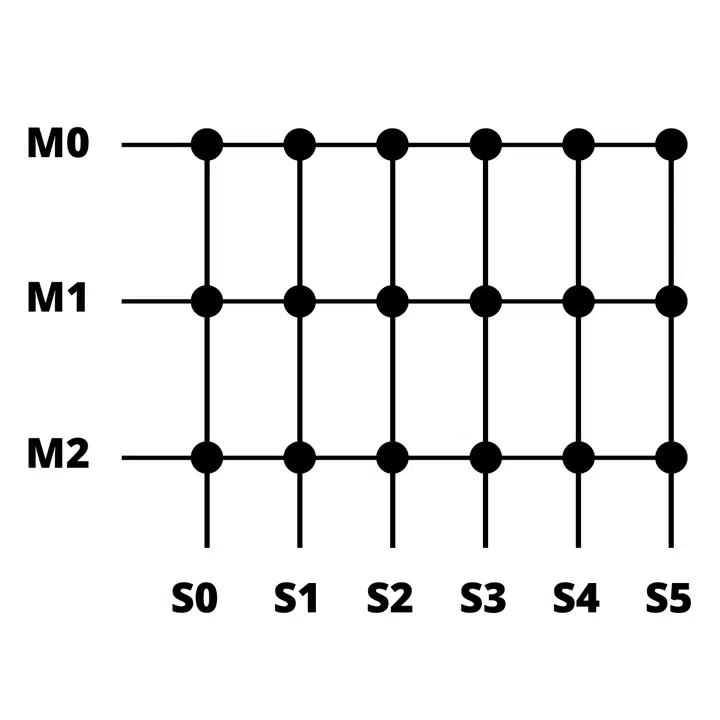

This VHDL module lets multiple Wishbone masters talk to multiple slaves simultaneously using a crossbar switch topology.

Description

Wishbone is an open-source hardware communication bus protocol.

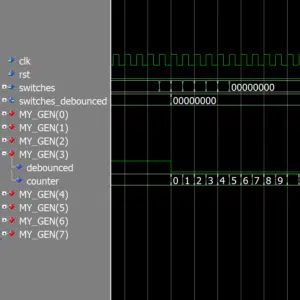

The downloadable demo project contains a complete testbench, which you can customize to simulate different numbers of masters and slaves communicating.

In the 40-minute video on the resource page, I will first show how to use and simulate the demo project. Then, in the second half of the video, I explain how the code works.

This project is a continuation of my earlier Wishbone course:

Course: Testbench reuse using VUnit and VHDL configurations for Wishbone bus verification

Refer to these links for the original Wishbone specification:

OpenCores – Wishbone, Revision B.4 Specification PDF

OpenCores – SoC Interconnection: Wishbone

The demo project also contains Wishbone master and slave synthesizable (RTL) modules, master and slave bus functional models (BFMs), and testbenches for those and the crossbar module itself.

The master and slave demo modules support pipelined block transfers, while the crossbar uses single-word transfer. The pipelined block devices can be connected but will be slowed down by the interconnect.

The testbenches use the VUnit open-source VHDL verification framework.

This project is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other VHDL resources and courses.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Entity of the Wishbone crossbar interconnect VHDL module

(You get the complete VHDL module in the downloadable Zip)

entity wb_crossbar is

port (

clk : in std_logic;

rst : in std_logic;

-- Masters

m_adr : in addr_array_t(masters_range);

m_dat_i : out data_array_t(masters_range);

m_dat_o : in data_array_t(masters_range);

m_cyc : in std_logic_vector(masters_range);

m_stb : in std_logic_vector(masters_range);

m_we : in std_logic_vector(masters_range);

m_stall : out std_logic_vector(masters_range);

m_ack : out std_logic_vector(masters_range);

-- Slaves

s_adr : out addr_array_t(slaves_range);

s_dat_i : out data_array_t(slaves_range);

s_dat_o : in data_array_t(slaves_range);

s_cyc : out std_logic_vector(slaves_range);

s_stb : out std_logic_vector(slaves_range);

s_we : out std_logic_vector(slaves_range);

s_stall : in std_logic_vector(slaves_range);

s_ack : in std_logic_vector(slaves_range)

);

end wb_crossbar;

Zip content

Here’s the list of files included in the project (plus a usage description video):

wishbone_crossbar/

├── common

│ ├── wb_32_1024_pkg.vhd

│ └── wb_pkg.vhd

├── crossbar

│ ├── wave.do

│ ├── wb_crossbar.vhd

│ ├── wb_crossbar_pkg.vhd

│ ├── wb_crossbar_pkg_user.vhd

│ └── wb_crossbar_tb.vhd

├── master

│ ├── wave.do

│ ├── wb_master.vhd

│ ├── wb_master_rtl_sim_wrapper.vhd

│ └── wb_master_tb.vhd

├── run.py

├── sim

│ ├── wave.do

│ ├── wb_master_bfm.vhd

│ ├── wb_slave_bfm.vhd

│ └── wb_tb.vhd

├── slave

│ ├── wave.do

│ ├── wb_slave.vhd

│ └── wb_slave_tb.vhd

├── system

│ ├── wave.do

│ └── wb_system_tb.vhd

└── vunit_bfms_only

├── vunit_bfms_tb.vhd

└── wave.do

This project is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other VHDL resources and courses.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.