VHDLwhiz Membership

$39This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

This content from the VHDLwhiz shop is suitable for intermediate users.

Showing 1–12 of 16 results

This subscription-based training program supports you in becoming successful in VHDL design. Join the community and build your confidence as an FPGA engineer.

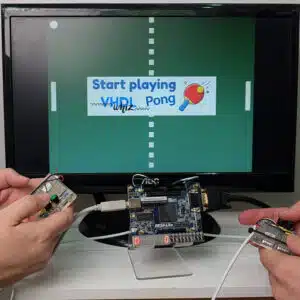

VHDL Pong game implementation course teaching how to control a VGA monitor from an FPGA, including sync signals, gameplay, and displaying images over VGA.

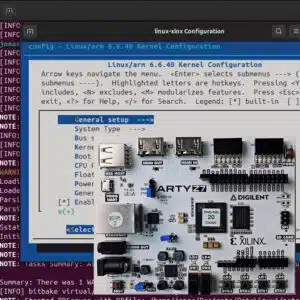

Learn to implement system-on-chip (SoC) designs using embedded Linux for AMD Xilinx FPGAs. This course gives you the skills to succeed with PetaLinux on Zynq-7000 (ARM) devices.

Learn to design and implement high-speed source-synchronous parallel data buses in FPGAs using VHDL.

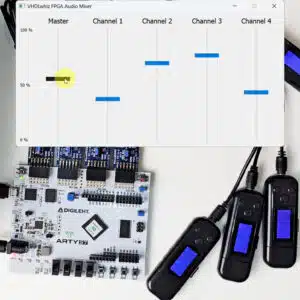

Learn to create a stereo audio mixer using VHDL and multiplier (DSP) primitives in an FPGA and use a Python GUI to control the four input channels.

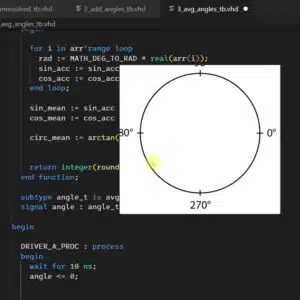

Learn how the std_logic type handles driver conflicts internally. See how to implement custom data types with resolution functions for multiple drivers.

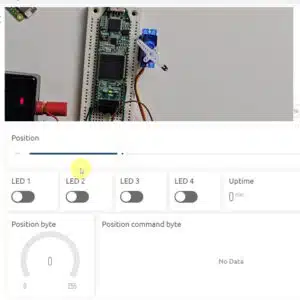

Bring your VHDL project online. Set up a neat GUI dashboard using the Blynk IoT platform and a Raspberry Pi and send over-the-air (OTA) updates to your FPGA.

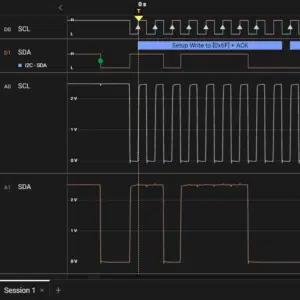

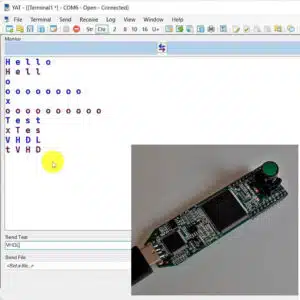

Learn to create an I²C controller (master) in VHDL and communicate with the Digilent Pmod RTCC: Real-time Clock / Calendar module.

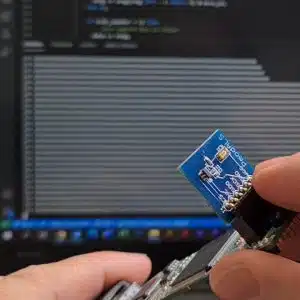

Learn to create an SPI master in VHDL for reading an ambient light sensor from an FPGA. We also make an SPI slave BFM for simulating the ADC chip.

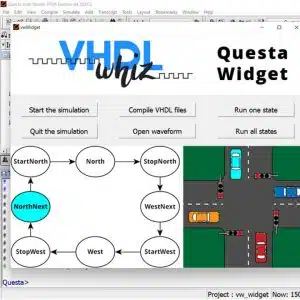

Learn the quirks of the Tool Command Language (Tcl) and see how to create a GUI widget for controlling a VHDL testbench in Questa/ModelSim.

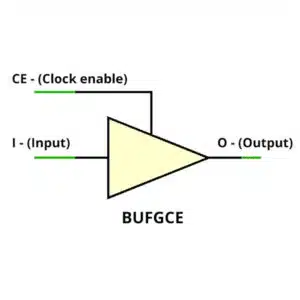

Learn to use Xilinx’s MMCMs to derive clocks, create a gated clock, and write a run-time configurable clock divider without sacrificing timing using the BUFGCE primitive.

Learn how to implement run-length compression in VHDL! We will create encoder and decoder modules, a self-checking testbench, and implement it on an FPGA board.

End of content

End of content