Course: Advanced BFM signaling and transaction-based TB

Build a testbench that separates bit-level logic into separate modules and uses a command interface to control executor processes.

Description

Regain control over those mile-long VHDL testbench files!

You probably wouldn’t put all the code in your RTL design’s top module, and the same principle should apply to your main testbench file.

Divide-and-conquer is an engineering paradigm that I live by. This course shows clever methods for splitting the testbench code over multiple files.

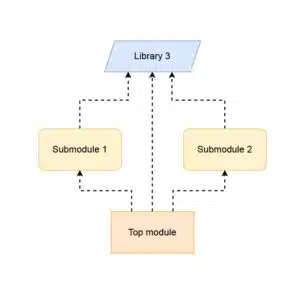

We’ll put the instances on one module, the checker processes in another, and create a package with procedures to control them. Then, in the main testbench, we only keep transaction-based logic.

Within it, a sequencer process will use procedure calls resembling commands to initiate checkers and bus functional models (BFMs) in the other testbench files.

This approach lets us keep the code in the main testbench file on a higher abstraction level than bit-level logic, ensuring you maintain a clear oversight in verification projects for intricate VHDL designs.

Please note that I sought inspiration (but didn’t copy) from the Universal VHDL Verification Methodology (UVVM) framework, which I recommend.

This course teaches methods that UVVM and other VHDL verification frameworks use internally. If you know how they work under the hood, learning to use them properly should be easier.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

No FPGA board is required as this course is a pure simulation exercise.

Software used in the course

I am using Windows 11 in the course. All the other software is available for free for Windows and Linux:

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do)

Course outline

The overview below shows the lessons in this course.

1 - Introduction

Welcome to the tutorial! You will learn advanced methods for splitting a testbench over multiple VHDL files.

2 - The example testbench project

Let me present the example project and self-checking testbench that we will improve in this tutorial series.

3 - Using the 'transaction attribute in BFMs

This neat trick utilizes a signal attribute to simplify testbench interfaces.

4 - TX BFM command queue

We will add a command queue to the TX_BFM module to further simplify its entity and remove the 'ready' signal.

5 - Communicate with checker processes using queues

We want only transaction-level code in the main sequencer. Let's move the bit-level stuff to different processes.

6 - Making use of procedures in the sequencer

Let's move the bit-level code in the sequencer process into subprograms with command-like names.

7 - Splitting the code over several VHDL files

Signals declared in a package is an alternative method of linking several testbench modules.

8 - Command interface and executors in different files

We can control multiple executor processes in a different module through a single interface by using this method.

9 - Using an overloaded procedure

We can overcome the limitation of subprograms in packages by declaring an overloaded version in the sequencer process.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.