Course: Protected type string list

Learn to create a dynamic string list in VHDL based on Python’s list class. Use a protected type to store any number of strings of any length during simulation.

Description

A protected type in VHDL is similar to a class in software languages like Java or Python.

There’s a reason why all modern programming languages rely on object-oriented design principles. It makes you more productive in the long run.

Encapsulating data and functions in a smart object removes much of the complexity from your main testbench file. That’s why notable VHDL libraries like UVVM and OSVVM consist of packages with protected types.

And you can use it too!

In this course, we create a new VHDL package and learn how to use VHDL’s class-like constructs in testbenches.

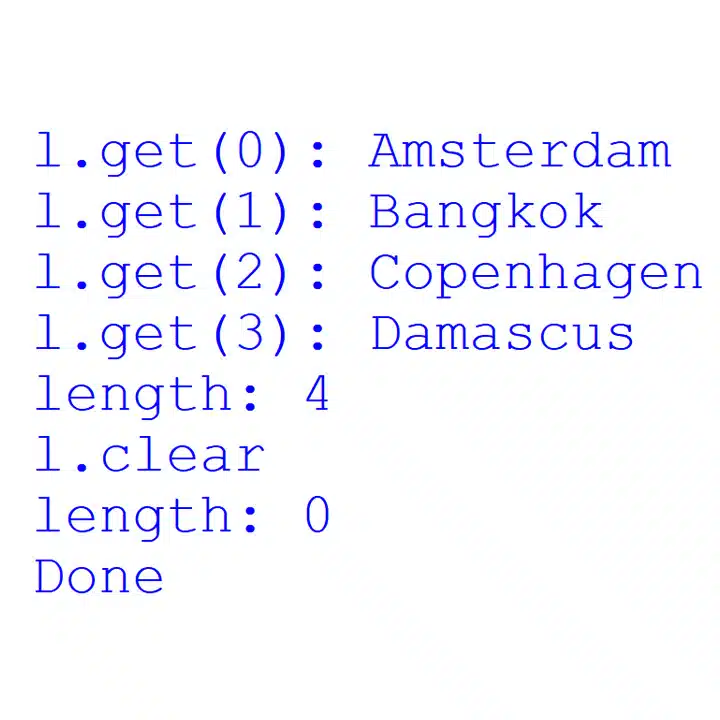

-- Add an item to the end of the list procedure append(str : string); -- Add an item to the list in a given position procedure insert(index : integer; str : string); -- Get an item from the list without deleting it impure function get(index : integer) return string; -- Remove an item from the list and free the memory it used procedure delete(index : integer); -- Delete all items from the list and free the memory procedure clear; -- Get the number of items in the list impure function length return integer;

We’ll implement a dynamic VHDL list of strings with the above subprograms, modeled after Python’s list class.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

No FPGA board is required as this course is a pure simulation exercise.

Software used in the course

I am using Windows in the course. All the other software is available for free for Windows and Linux:

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do)

Course outline

The overview below shows the lessons in this course.

1 - Project setup

Create the testbench and ModelSim project using resource templates.

2 - Fixed-length string array

Implement a regular fixed-length, fixed-width string array in VHDL.

3 - Python's list class

Examine Python's list class, which we will mimic in our dynamic VHDL string list.

4 - Subprogram prototypes

Declare the subprogram prototypes in the protected type's declarative region.

5 - Data structure

Define the types and variables to store the strings in a linked list topology.

6 - Insert procedure

Implement the procedure that inserts a string at any position of the list.

7 - Translate negative indexes

Modify the insert procedure to accept negative index arguments.

8 - Get function

Write the get function that's the equivalent of Python's array operator.

9 - Delete procedure

Use helper functions when creating the procedure that deletes strings from the list.

10 - Length, clear, and append

Fill in the missing implementations for these subprograms.

11 - Example testbench

Let's modify an example testbench from the resource library to use our new dynamic VHDL string list!

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.