VHDL package: Binary file reader/writer

$29

These VHDL packages provide a user-friendly interface for binary file access in simulation to read or write bit vectors of any length.

Description

This project contains two VHDL packages for reading from or writing binary data to files in simulation.

The new packages’ protected types (VHDL classes) provide a more straightforward interface for file access than VHDL’s standard TEXTIO package. Additionally, it allows for uncomplicated reading and writing of data chunks with arbitrary bit lengths.

It’s useful for testbenches operating on binary files where the information fields don’t fit into byte boundaries, for example, image files or network packages.

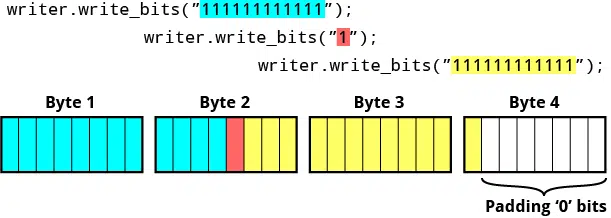

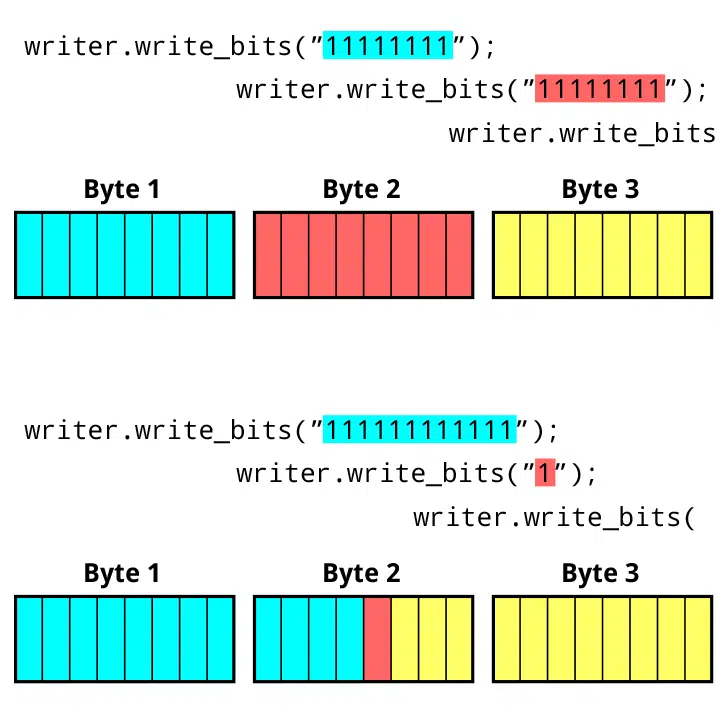

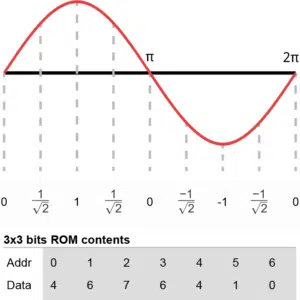

You can store single bytes or different vector lengths, as shown in the illustration below.

Refer to the user manual PDF for more use cases and descriptions of using these file reader/writer packages.

Click here to download the Binary file RW packages – User Manual:

This project is also available in the VHDLwhiz Membership.

The difference is that when you purchase this product, you get immediate access to the downloadable Zip file, while the membership charges a monthly fee to access the content.

file_reader_pkg.vhd

The code listing below shows the declarative region of the file reader package.

package file_reader_pkg is

type file_reader is protected

-- Open the binary file for reading

--

-- @param filename The path to the input file

--

procedure open_file(filename : string);

-- Close the binary file if open

procedure close_file;

-- Check if the file has been opened for reading

--

-- @return true if the file is open

--

impure function is_open return boolean;

-- Check if more data is available for reading from the file

--

-- @param min_bits_left The number of bits in the next potential read.

-- Values > 8 default to 8 (one byte).

-- The function has to know if the next expected read size is less than

-- one byte to determine if the remaining bits are padding or data bits.

--

-- @return true if there are at least'min_bits_left' bits left to read

--

impure function is_empty(min_bits_left : integer := 8) return boolean;

-- Read from the input file

--

-- @param n_bits The number of bits to read from the file

--

-- @return A vector containing the read bits

--

impure function read_bits(n_bits : integer) return std_logic_vector;

-- Read from the input file.

-- This procedure does the same as the read_bits function,

-- but the procedure only works when assigning to a variable.

--

-- @param bits The vector to put the read bits into.

-- The procedure will read bits'length number of bits from the file.

--

procedure read_bits(variable bits : out std_logic_vector);

end protected;

end package;

file_writer_pkg.vhd

The code listing below shows the declarative region of the file writer package.

package file_writer_pkg is

type file_writer is protected

-- Open the binary file for writing

--

-- If the file exists, it will be overwritten.

--

-- @param filename The path to the input file

--

procedure open_file(filename : string);

-- Close the output file if open

--

-- Before exiting the simulation,

-- you must call this method to ensure that every bit gets written.

--

-- If the total number of written bits is not a multiple of 8,

-- the output file will be padded with zero bits in the final byte.

procedure close_file;

-- Check if the file has been opened for writing

--

-- @return true if the file is open

--

impure function is_open return boolean;

-- Write data to the output file

--

-- @param bits The vector containing the data to write.

-- Every bit from the bits vector will be written to file.

--

procedure write_bits(bits : in std_logic_vector);

end protected;

end package;

License agreement

MIT License

Copyright (c) 2026 Jonas Julian Jensen

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Reviews

There are no reviews yet.