Course: Script-based workflow

Learn how to structure a VHDL project with multiple submodules. Use scripts to derive the compile order, launch simulations, and run regression tests.

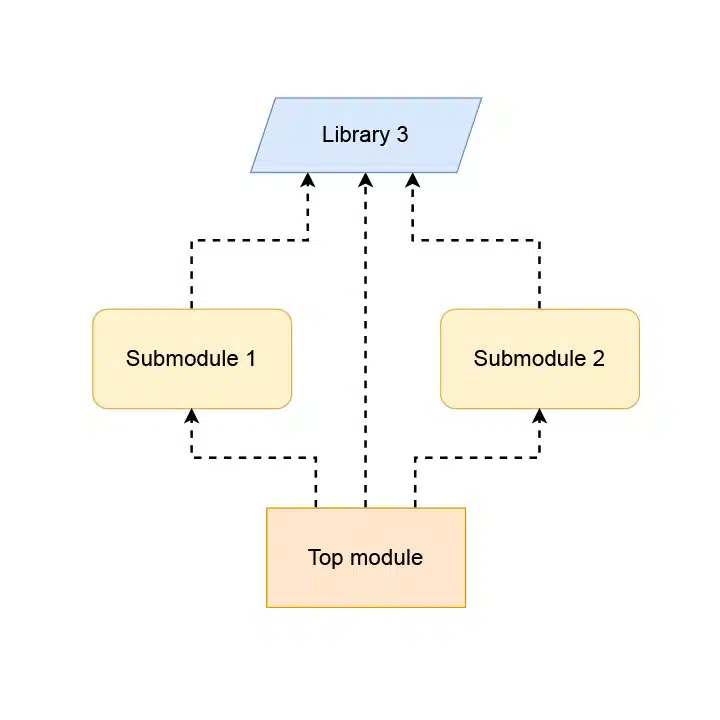

Description

If you plan to develop an ecosystem of VHDL modules, think through how to organize them. You will inevitably have to make some principal design decisions.

At least, you should choose a flat or a hierarchical project structure. It has implications for what you must include in the submodules and what goes into the main FPGA projects.

This course is a continuation of one previously published in the membership:

Course: Makefile-based workflow for Lattice

I’m teaching creating a script-based design flow using a flat project structure. All submodules appear only once in your project folder, even if several modules depend on them.

Furthermore, we use a Python script to automatically derive the compile order for simulation and implementation.

Finally, we create a regression Makefile target that runs all testbenches in your design — a necessity to avoid breaking something else when you make changes to a module that’s used in many places.

With the completed Makefile, you can manage your FPGA project from the command line with multiple make targets, including:

- make synth to synthesize

- make hw to generate the bitfile

- make prog to program the FPGA

- make sim to simulate in batch mode

- make simgui to simulate in the Questa GUI

- make regression to run a regression test on all submodules

You are free to use my scripts and Makefiles in your company as you please, but you may want to make some changes. There’s no one-size-fits-all when it comes to project structure. Everyone’s needs and priorities differ slightly, but the challenges are the same.

This course shows you one possible solution to make you understand the concepts so that you can create a setup you are happy with.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Hardware used in the course

Software used in the course

I am using Windows in the course. All the other software is available for free for Windows and Linux:

⚠ Notice: free educational license required

Lattice Semiconductor now charges over $350/year for the iCEcube2 software.

Fortunately, VHDLwhiz, in cooperation with Lattice, offers a 1-year educational license for iCEcube2 to customers who purchase a course that uses the iCE40 FPGA.

Reply to the purchase confirmation email to request a free license.

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Lattice iCEcube2 Design Software

(Or the implementation software for your FPGA architecture) - Microsoft Visual Studio Code

(Any editor will do) - The GNU Make tool

Installed through Chocolatey in Windows or pre-installed in Linux - Git SCM

- A Python3 interpreter

Course outline

The overview below shows the lessons in this course.

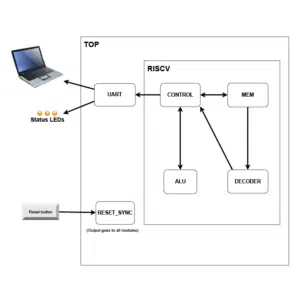

1 - Introduction

The previous tutorial series:Makefile-based workflow for Lattice

2 - Flat vs. hierarchical project structure

The way your build scripts work has implications for how you need to organize your VHDL repositories.

3 - Setting up the directory structure

Let's convert the project to use a flat structure with testbenches for each submodule.

4 - ModelSim batch mode commands

These are the ModelSim commands we will use in our scripts.

5 - Auto-generated Makefile

Let's derive the compile order dynamically using a script.

6 - Simulation Makefile targets

It's time to create the 'sim' and 'simgui' Makefile targets.

7 - Submodule Makefiles

Every submodule's Makefile in a flat project structure needs to reference the main project's Makefile.

8 - Regression test

Prevent breaking other components by running all testbenches after you change something in one module.

9 - Clean and help targets

Every Makefile should have a 'clean' target that resets the project to the state it was in before you ran Make.

10 - Auto-generated implementation file list

Let's write some Tcl code to read the synthesis compile order from file.

11 - Wrapping it up

Let's do a quick recap of what we learned in this tutorial series.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.