Course: Constrained random verification with OSVVM

Learn to achieve functional coverage in VHDL testbenches with pseudo-random DUT interactions by using the OSVVM VHDL framework.

Description

This course teaches how to use the constrained random verification (CRV) strategy in VHDL testbenches.

See my free article for more information about CRV:

VHDLwhiz article: Constrained random verification

CRV uses algorithms to generate pseudo-random test vectors, unlike the traditional directed testing strategy that runs through a predefined test sequence. Instead of manually crafting the tests to hit corner cases, we let the testbench randomly interact with the device under test (DUT).

Simultaneously, we monitor the transactions from a different process or module. When the random interactions with the DUT hit a corner case that we want to test, we record that in a scoreboard.

Finally, we stop the simulation when all corner cases have been hit.

We will use the Open Source VHDL Verification Methodology (OSVVM) framework to implement the randomization, scoreboards, intelligent coverage generation, and printouts to the simulator transcript.

VHDLwhiz is not affiliated with or endorsed by the OSVVM team or SynthWorks Design Inc.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

No FPGA board is required as this course is a pure simulation exercise.

Software used in the course

I am using Windows in the course. All the other software is available for free for Windows and Linux:

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Microsoft Visual Studio Code

(Any editor will do) - Open Source VHDL Verification Methodology (OSVVM)

Course outline

The overview below shows the lessons in this course.

1 - What is CRV?

Constrained random verification (CRV) is a testbench strategy that relies on randomization to achieve functional coverage.

2 - Example project

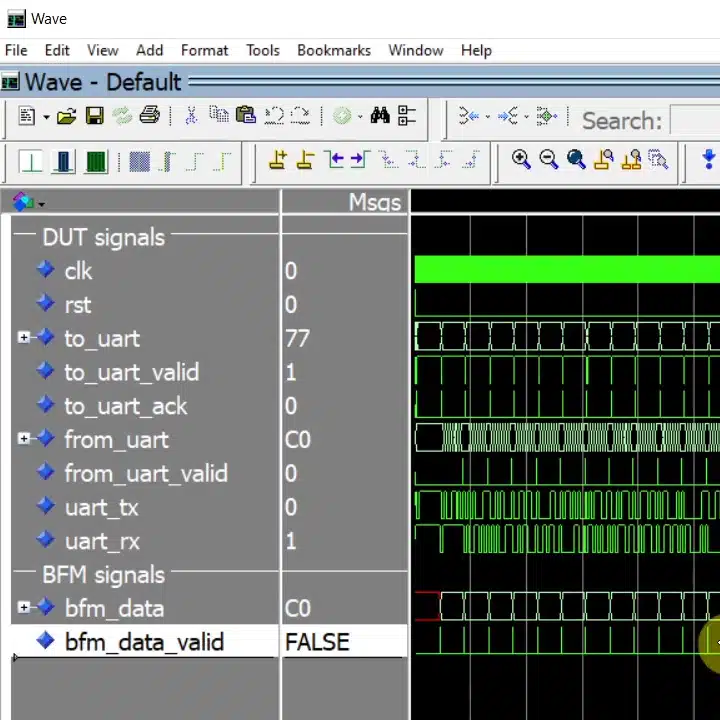

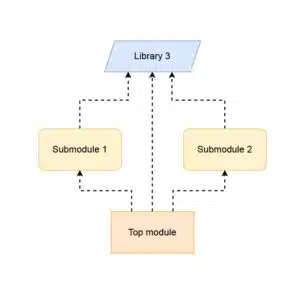

The downloadable Zip file contains the DUT UART module, the OSVVM library, and the starting point for our CRV testbench.

3 - Instantiate the DUT

Start on the testbench by instantiating the UART module that we want to check.

4 - First interaction with the DUT

Let's create a process that continuously feeds the UART module with random input data.

5 - Instantiate the BFM

We will compare the DUT's behavior to a bus functional model (BFM) of a UART.

6 - ScoreboardPkg for checking the DUT's output

OSVVM ships with a convenient package for implementing testbench FIFOs.

7 - CoveragePkg for capturing functional coverage points

Functional coverage is one of the pillars of the OSVVM methodology.

8 - Intelligent coverage randomization

Let's wrap up this testbench by using CoveragePkg's GetRandPoint function to pick the random bytes.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.