Course: Numeric types

There are many beliefs about using numeric types like signed, unsigned, integer, and real in VHDL. Let’s find out precisely what the limitations are!

Description

Some say that you should not use integer or real types at all in RTL code (code that goes on the FPGA), while others say we can if we follow certain design rules.

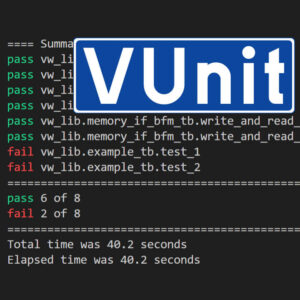

To find out once and for all, I will play MythBusters and run some example modules through four of the most popular VHDL synthesis tools.

Lesson 2. talks about how FPGAs store unsigned and signed integers. Many of you already know about two’s compliment, but it’s essential knowledge that everyone needs to understand before we can proceed.

Lesson 3. is where the fun starts for intermediate and advanced learners. We will find out if integer types are safe for synthesis and what happens if we don’t specify the ranges.

Lesson 4. covers the crucial difference between a cast and a conversion. One changes how we interpret bits, while the other may alter the data.

Lesson 5. is where we get real (😅😅)! More specifically, we will get values from an array of real type elements in an RTL module. Will it work?

Lesson 6. talks about non-standard packages that operate on unsigned and signed types. We can do math with std_logic_vectors without conversion. But is it a good idea?

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

You don’t need an FPGA board to do this course because we don’t actually use any hardware.

Software used in the course

I am using Windows in the course. All the other software is available for free for Windows and Linux:

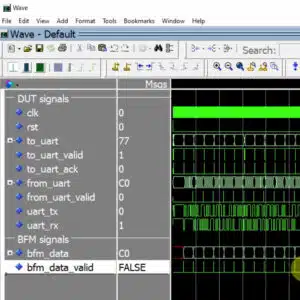

- Questa – Intel FPGA Edition(includes Starter Edition)

(Any version of ModelSim or QuestaSim will work) - Xilinx Vivado

- Intel Quartus Prime Lite Edition

- Lattice iCEcube2 Design Software

(To test in the Synplify Pro synthesizer that comes with iCEcube2) - Lattice Diamond Software

(To test in the Lattice synthesis engine that comes with Diamond) - Microsoft Visual Studio Code

(Any editor will do)

You only need to install the above programs if you want to experiment on your own.

Course outline

The overview below shows the lessons in this course.

1 - Introduction

Let's find out how we can and cannot use numeric types in RTL code.

2 - Signed and unsigned

Understanding how negative integer numbers are stored using two's complement is essential.

3 - Integers

Are integers safe for synthesis? Let's find out!

4 - Cast vs. conversion

A cast only changes the way we interpret the data, while conversion may result in restructuring and precision loss.

5 - Real

You can use floating-point types in RTL code if their values convert to representable types during synthesis.

6 - Non-standard packages

The IEEE 1076.3 standard deprecates some older packages defining numeric types.

This course is only available in the VHDLwhiz Membership.

The membership subscription gives you access to this and many other courses and VHDL resources.

You pay monthly to access the membership and can cancel the automatic renewal anytime. There is no lock-in period or hidden fees.

Reviews

There are no reviews yet.