Course: Script-based workflow

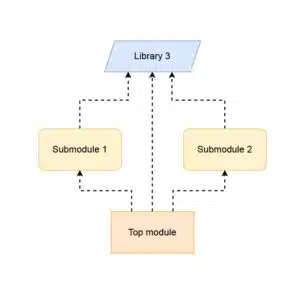

Learn how to structure a VHDL project with multiple submodules. Use scripts to derive the compile order, launch simulations, and run regression tests.

Showing 37–48 of 57 results

Learn how to structure a VHDL project with multiple submodules. Use scripts to derive the compile order, launch simulations, and run regression tests.

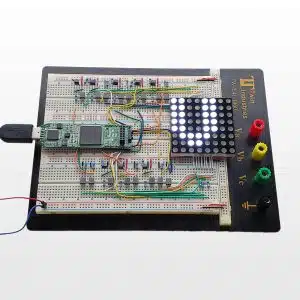

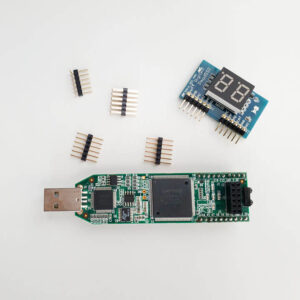

Learn how to create a VHDL project from scratch with self-checking testbenches. Dot Matrix is the most extensive course VHDLwhiz has ever made.

Hands-On for Absolute Beginners. Understand the basics of FPGA development using VHDL in a few evenings!

VHDL testbench boilerplates verifying the same UART receiver using plain VHDL, VUnit, UVVM, and OSVVM. Includes Questa project files and walkthrough videos.

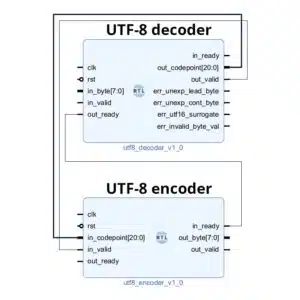

UTF-8 decoder and encoder modules that let your text-processing VHDL project operate on 21-bit Unicode code points instead of variable-length byte streams.

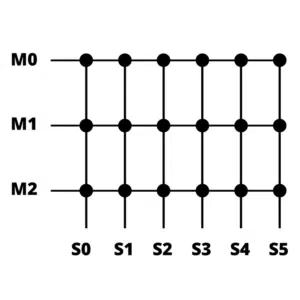

This VHDL module lets multiple Wishbone masters talk to multiple slaves simultaneously using a crossbar switch topology.

This demo project contains five VHDL implementations of two hardware-friendly sorting algorithms: (Odd-even) Brick sort and Selection sort.

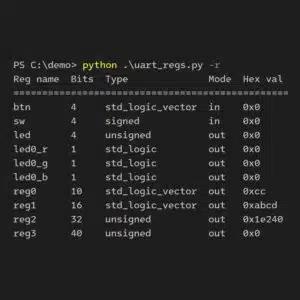

This tool generates a VHDL module and a Python script to read from or write to any number of custom FPGA registers using UART.

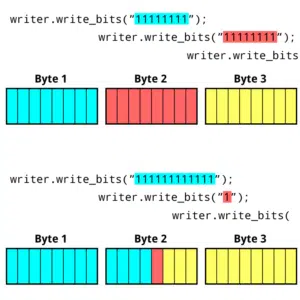

These VHDL packages provide a user-friendly interface for binary file access in simulation to read or write bit vectors of any length.

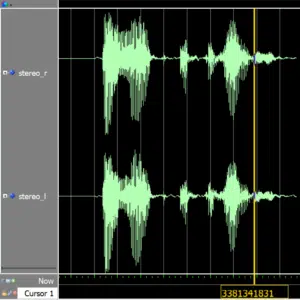

These VHDL packages read and write WAV audio files. They provide a user-friendly way to run VHDL simulations on audio processing modules.

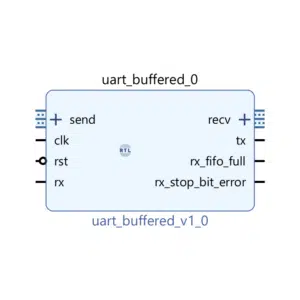

This project contains three general-purpose, AXI compatible, universal asynchronous receiver-transmitter (UART) modules.

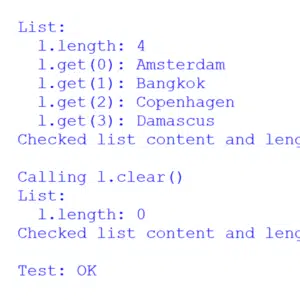

This VHDL package can store any data type in dynamic memory. It mimics the behavior of Python’s list class and supports negative indexing.

End of content

End of content