I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Should I learn VHDL if Verilog is becoming more popular?

Which HDL is the most popular, and should I learn VHDL or Verilog? That’s a question I often get asked, and it’s understandable. People want to future-proof their learning by betting on the winning horse. But which one is it, and does it matter?

How to use Wait On and Wait Until in VHDL

In the previous tutorial we learned the main differences between signals and variables. We learned that signals have a broader scope than variables, which are only accessible within one process. So how can we use signals for communication between several processes? We have already learned to use wait; to wait infinitely, and wait for to…

Basic VHDL quiz

Have fun and learn from this VHDL and FPGA design quiz with 28 questions for beginners and intermediate learners in random order.

All questions include an explanation for the correct answer that will be shown after you make your selection.

How a signal is different from a variable in VHDL

In the previous tutorial we learned how to declare a variable in a process. Variables are good for creating algorithms within a process, but they are not accessible to the outside world. If a scope of a variable is only within a single process, how can it interact with any other logic? The solution for…

How to use a function in VHDL

Functions are subprograms in VHDL which can be used for implementing frequently used algorithms. A function takes zero or more input values, and it always returns a value. In addition to the return value, what sets a function apart from a procedure, is that it cannot contain Wait-statements. This means that functions always consume zero…

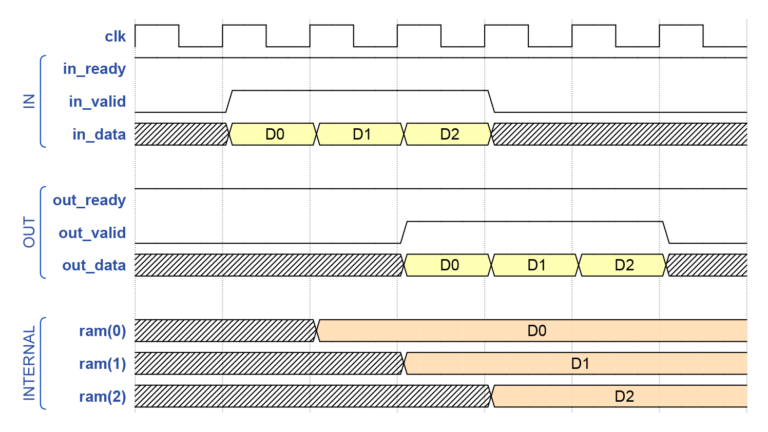

How to make an AXI FIFO in block RAM using the ready/valid handshake

I was a little annoyed by the peculiarities of the AXI interface the first time I had to create logic to interface an AXI module. Instead of the regular busy/valid, full/valid, or empty/valid control signals, the AXI interface uses two control signals named “ready” and “valid”. My frustration soon changed to awe. The AXI interface…

First of all, thank you so very much!

These are by far the most comprehensible tutorials I have come across like ever!

Brilliant work.

So here my two cents out of gratitude:

Basic VHDL Quiz – part 4

Which statement is not true?

Answer 3 : The return statement cannot be omitted.

-> Correct

So the return statement CAN be omitted???

“Unlike in most other programming languages, the return keyword is mandatory in functions in VHDL.”

Confused by double negation. Me or you 😉

Good catch! I’ve changed the answer now. I was trying to make you think, but in the process I confused myself too 🙂

“The return-keyword cannot be used in a procedure”. I believe that this is incorrect, e.g.

https://web.archive.org/web/20200629023040/http://vhdl.renerta.com:80/source/vhd00060.htm

It is true, of course, that you cannot return a value with it, that’s the only (?) difference between procedures and functions. But, as in other languages, you can use “return” as control flow statement to “force an exit”.

You are right! I missed the possibility of using return statements in procedures without returning a value. According to the Renata link you posted, functions must return a value, while procedures can have return statements, but then without a return value.

I am changing this question.