I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

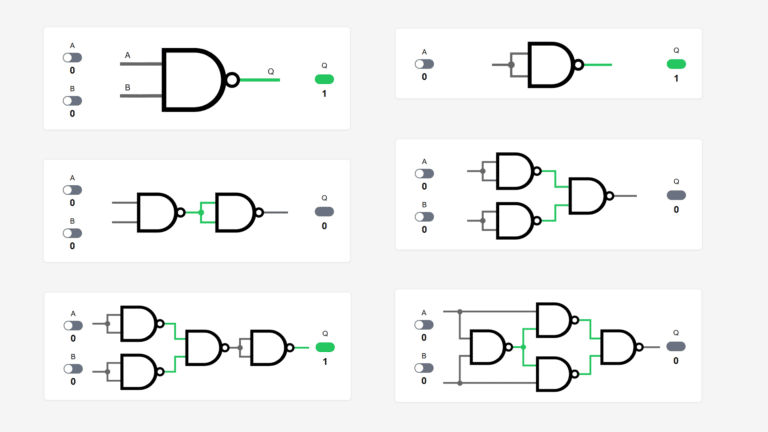

NOR logic gates interactive demo

Did you know that you can construct any other digital logic gate using only NOR gates? You can also do it with NAND logic. That’s why we say that these two are universal gates. This article shows one way to implement every logic gate using NOR logic, and the schematics are interactive, like a logic…

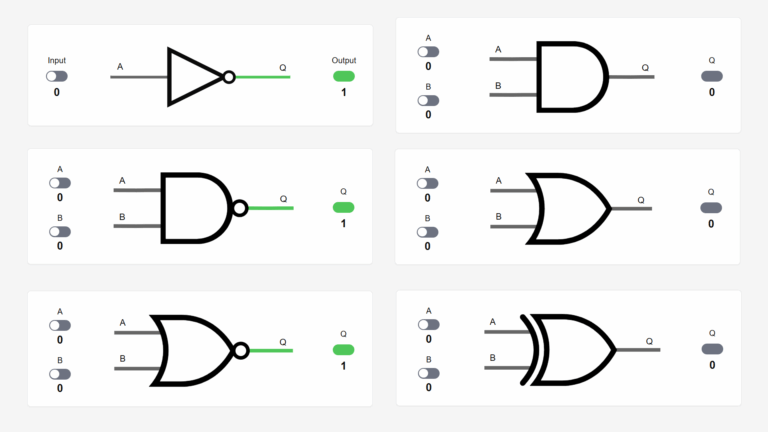

Logic gates interactive demo

The basic logic gates NOT, AND, NAND, OR, NOR, XOR, and XNOR are fundamental building blocks in digital circuits corresponding to Boolean operators.

Play with the switches to see how the outputs change! 😀

Basic VHDL quiz – Part 4

Test your progress with this VHDL quiz after completing part 4 of the Basic VHDL Tutorial series!

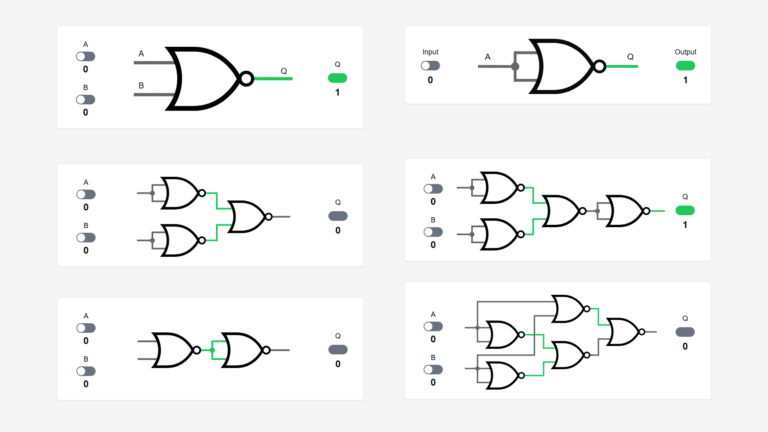

NAND logic gates interactive demo

We can construct any other digital logic gate using only NAND gates as building blocks. This is why NAND is known as a universal gate. NAND logic is widely used as the foundation for designing digital circuits in modern integrated chips. Actually, NOR is also a universal gate, but NAND logic is more prevalent than…

Basic VHDL quiz – Part 3

Test your progress with this VHDL quiz after completing tutorials 12-17 from the Basic VHDL Tutorial series!

Basic VHDL quiz – Part 1

Put your skills to the test with this quiz with questions from the first part of the Basic VHDL Tutorial series.

very good