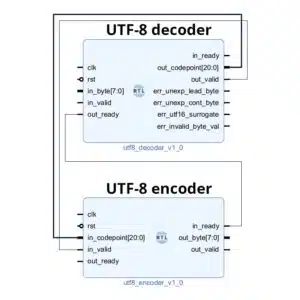

VHDL module: Unicode (UTF-8) decoder and encoder

UTF-8 decoder and encoder modules that let your text-processing VHDL project operate on 21-bit Unicode code points instead of variable-length byte streams.

Showing all 12 results

UTF-8 decoder and encoder modules that let your text-processing VHDL project operate on 21-bit Unicode code points instead of variable-length byte streams.

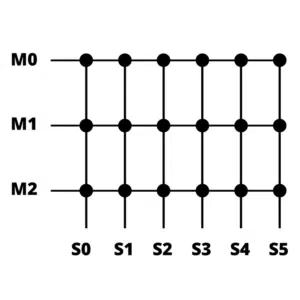

This VHDL module lets multiple Wishbone masters talk to multiple slaves simultaneously using a crossbar switch topology.

This demo project contains five VHDL implementations of two hardware-friendly sorting algorithms: (Odd-even) Brick sort and Selection sort.

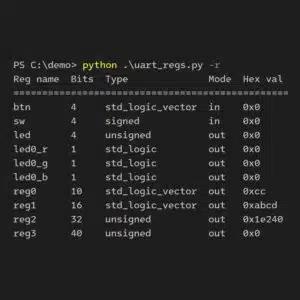

This tool generates a VHDL module and a Python script to read from or write to any number of custom FPGA registers using UART.

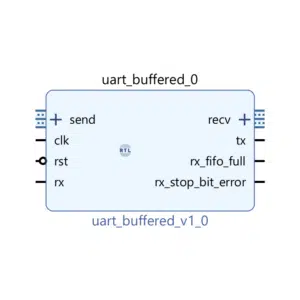

This project contains three general-purpose, AXI compatible, universal asynchronous receiver-transmitter (UART) modules.

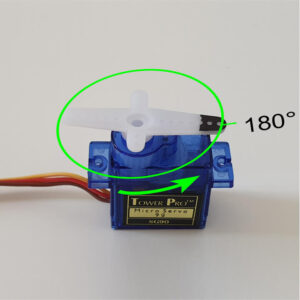

This VHDL module controls the position of an RC servo like the TowerPro SG90 motor using pulse-width modulation (PWM).

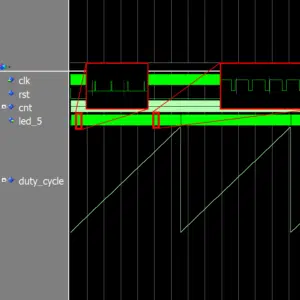

This VHDL module generates a pulse-width modulation (PWM) signal with generic counter length and run-time configurable frequency.

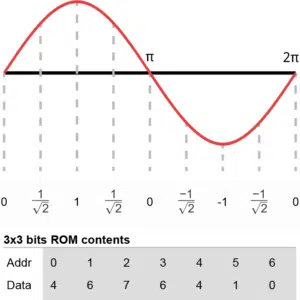

This VHDL module reads pre-calculated values from block RAM in the FPGA to generate a smooth sine wave pattern on the output signal.

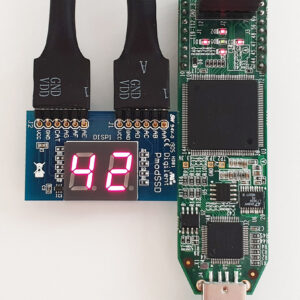

This VHDL module shows a decimal value from 0 to 99 on the Pmod SSD: Seven-segment Display from Digilent or similar dual 7-segment display.

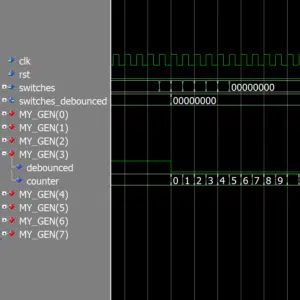

This VHDL project contains three modules that can debounce a switch or a button or arrays of them using a generate statement.

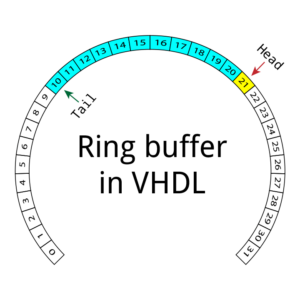

This VHDL implementation of a ring buffer FIFO has generic data width and depth settings.

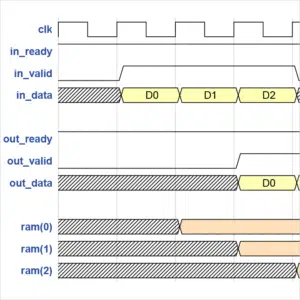

This VHDL implementation of an AXI-style FIFO has generic data width and depth settings.

End of content

End of content