Course: UVVM introduction

The Universal VHDL Verification Methodology (UVVM) framework provides a utility library, reusable verification components, and a way to structure your VHDL testbenches.

These are the paid/premium products in the VHDLwhiz shop.

Showing 25–36 of 48 results

The Universal VHDL Verification Methodology (UVVM) framework provides a utility library, reusable verification components, and a way to structure your VHDL testbenches.

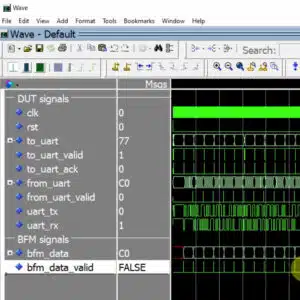

Build a testbench that separates bit-level logic into separate modules and uses a command interface to control executor processes.

Learn to achieve functional coverage in VHDL testbenches with pseudo-random DUT interactions by using the OSVVM VHDL framework.

Learn to develop high-speed image processing systems using VHDL. See how to simulate pixel filters using JPG pictures in a VHDL testbench.

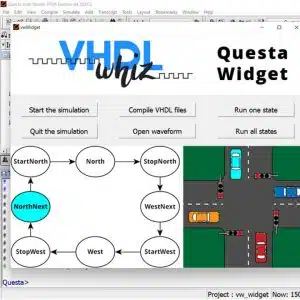

Learn the quirks of the Tool Command Language (Tcl) and see how to create a GUI widget for controlling a VHDL testbench in Questa/ModelSim.

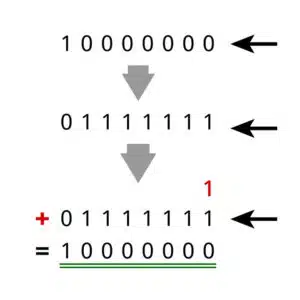

There are many beliefs about using numeric types like signed, unsigned, integer, and real in VHDL. Let’s find out precisely what the limitations are!

FPGA projects are challenging to debug, and that’s because it’s hard to understand what’s going on in the design. But once we gain insight and see the complete picture, problems often melt away.

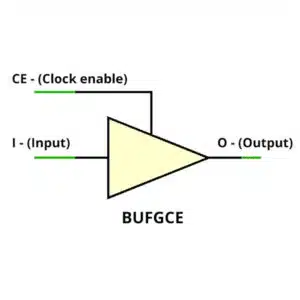

Learn to use Xilinx’s MMCMs to derive clocks, create a gated clock, and write a run-time configurable clock divider without sacrificing timing using the BUFGCE primitive.

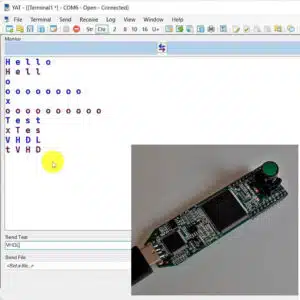

Learn how to implement run-length compression in VHDL! We will create encoder and decoder modules, a self-checking testbench, and implement it on an FPGA board.

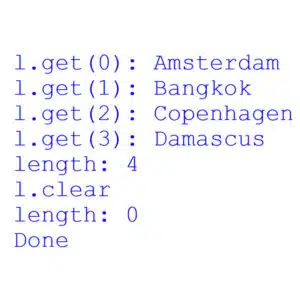

Learn to create a dynamic string list in VHDL based on Python’s list class. Use a protected type to store any number of strings of any length during simulation.

Understanding how delta cycles work in VHDL is key to becoming proficient in FPGA design. This course teaches you how signal scheduling works in simulation.

Learn to convert a Lattice iCEcube2 GUI project into a Makefile-based workflow. Manage your FPGA implementation project entirely from the command line.

End of content

End of content