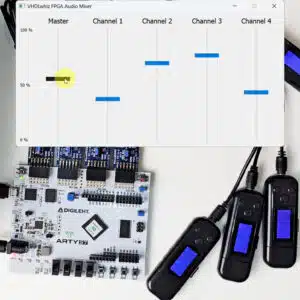

Course: VHDL audio mixer using FPGA DSP blocks

Learn to create a stereo audio mixer using VHDL and multiplier (DSP) primitives in an FPGA and use a Python GUI to control the four input channels.

These are the paid/premium products in the VHDLwhiz shop.

Showing 13–24 of 50 results

Learn to create a stereo audio mixer using VHDL and multiplier (DSP) primitives in an FPGA and use a Python GUI to control the four input channels.

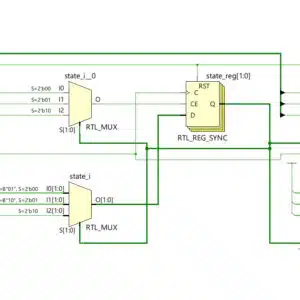

Learn to recognize which logic elements common VHDL design patterns describe. Think like an FPGA engineer by focusing on the underlying hardware rather than code.

Learn to use guarded blocks to disconnect signal drivers conditionally, and VHDL features like postponed processes and delay modeling mechanisms.

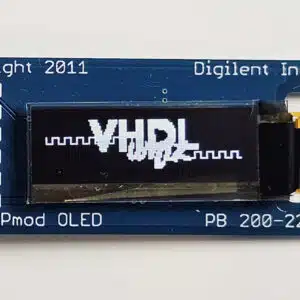

Connect an LED panel to your FPGA design to show messages or images. See how to read pixel data from a file into block RAM using VHDL.

Learn how the std_logic type handles driver conflicts internally. See how to implement custom data types with resolution functions for multiple drivers.

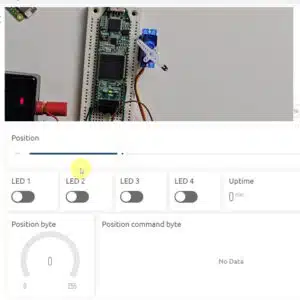

Bring your VHDL project online. Set up a neat GUI dashboard using the Blynk IoT platform and a Raspberry Pi and send over-the-air (OTA) updates to your FPGA.

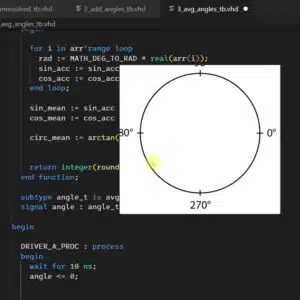

Write testbenches in Python for your VHDL design with the Cocotb hardware verification framework. Learn to use Python’s asynchronous constructs in the Questa and GHDL simulators.

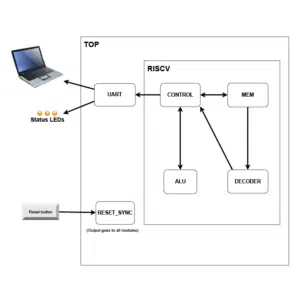

Create a reduced instruction set computer using the RISC-V processor architecture. Learn how a CPU works by implementing one in VHDL and running it on the FPGA.

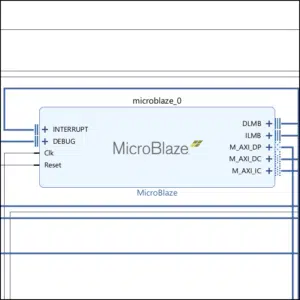

Learn how to build a system-on-chip (SoC) design by using a MicroBlaze soft-core processor, existing IP cores, and custom VHDL modules.

Learn to implement the I²S protocol in VHDL and configure the ADAU1761 ADC/DAC audio codec chip on the Xilinx Zedboard with bare-metal C programming.

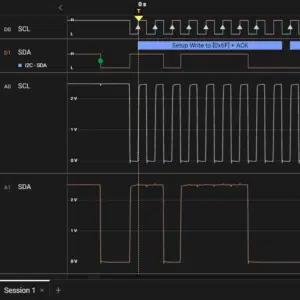

Learn to create an I²C controller (master) in VHDL and communicate with the Digilent Pmod RTCC: Real-time Clock / Calendar module.

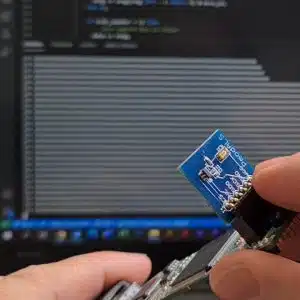

Learn to create an SPI master in VHDL for reading an ambient light sensor from an FPGA. We also make an SPI slave BFM for simulating the ADC chip.

End of content

End of content