Which HDL is the most popular, and should I learn VHDL or Verilog?

That’s a question I often get asked, and it’s understandable. People want to future-proof their learning by betting on the winning horse.

But which one is it, and does it matter?

As the author of this blog, I am, of course, very biased toward VHDL. But I will do my best to provide neutral data points and considerations you can use to make up your mind.

Is VHDL or Verilog more popular?

The first question we need to address is whether or not Verilog is becoming more popular than VHDL. I’ve heard such claims since I started using VHDL 10-15 years ago, and I can see how you would get that impression.

Tool vendors like to promote Verilog over VHDL. If you get all your information from them, you will see more code and documentation about Verilog. The community’s consensus is that this is because the vendors have economic incentives.

They can make more money from a Verilog user because SystemVerilog simulator licenses cost much more than VHDL simulators, where the free version often is sufficient.

Of course, they will try to convince you to use SystemVerilog’s UVM instead of VHDL’s free and open-source OSVVM and UVVM frameworks. It’s Marketing 101!

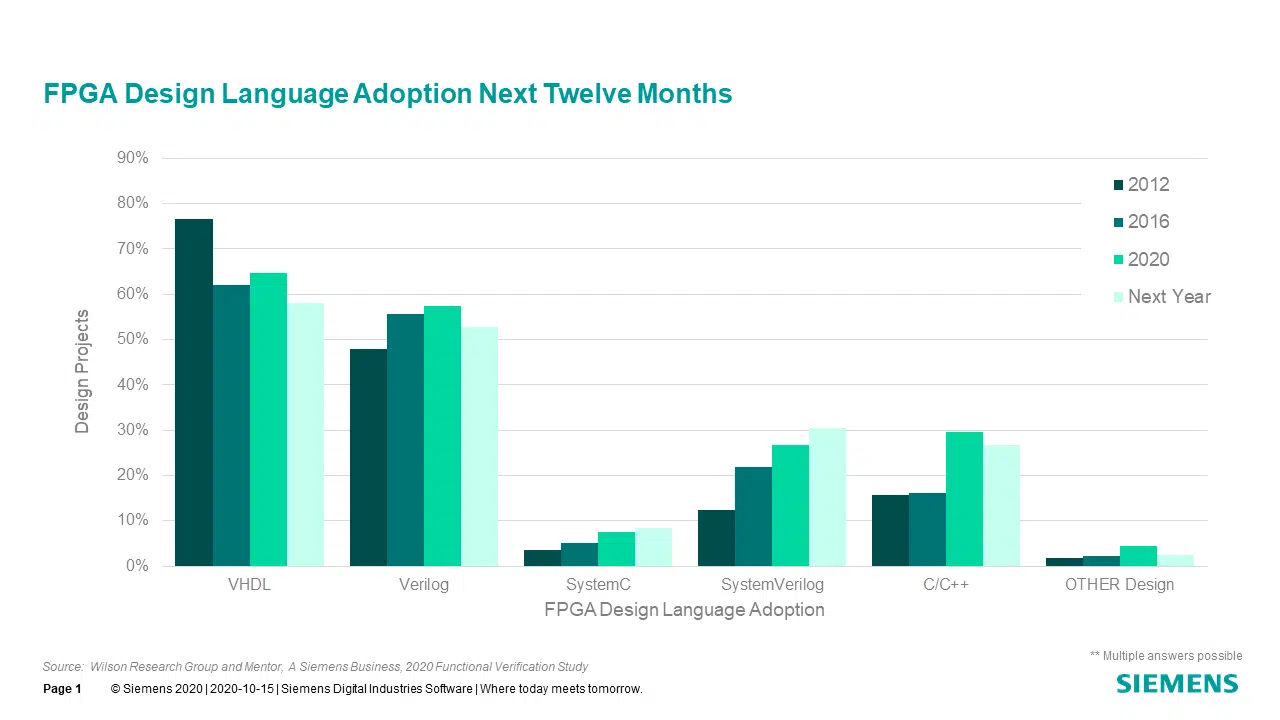

The functional verification study

There are many opinions but few empirical sources from which to derive VHDL versus Verilog popularity. However, one often cited source when talking about this matter is the Wilson Research Group Functional Verification Study (the 2020 publication is the latest available at the time of writing).

* Update December 6, 2022:

The 2022 functional verification study is now available, and it shows that VHDL is still the most popular HDL for FPGA design and verification, increasing in popularity from the 2018 study:

Part 6: The 2022 Wilson Research Group Functional Verification Study – FPGA Language and Library Trends

It’s sponsored by Mentor (Siemens), the company behind the Questa and ModelSim simulators. But they claim that the study pool isn’t based on Mentor’s customer list and that the confidence interval is 95%. I don’t think we can find more accurate numbers than that.

The most interesting section in this context is Part 6: FPGA Language and Library Trends.

The chart above shows the worldwide language usage for new FPGA projects, and VHDL is still the most popular HDL for RTL design.

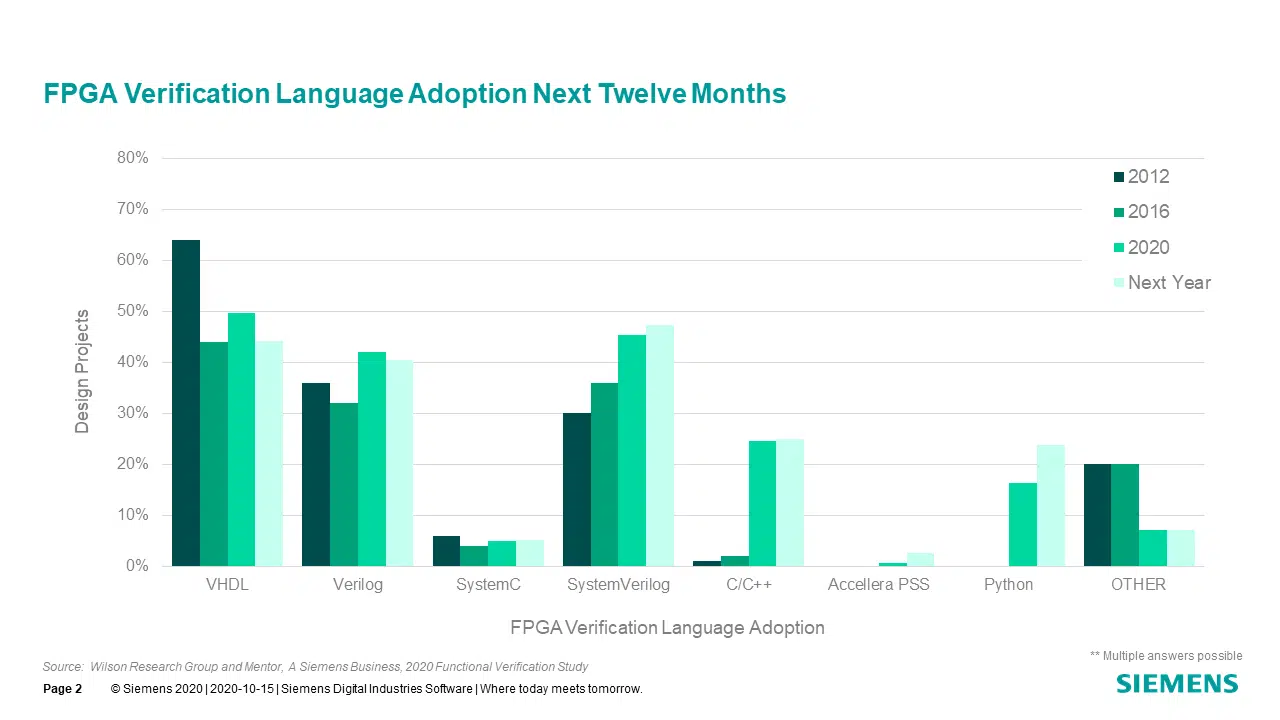

According to the chart below, VHDL is still more widely used for verification than Verilog, but SystemVerilog is the language most companies reported using for new verification projects next year (2021).

Furthermore, the study’s author writes (source):

It is important to note that the language adoption trends shown in fig. 6-1 are aggregated across all market segments and all regions of the world. When we filter the participants down to a specific region (e.g., Europe), or a specific market segment (e.g., Mil/Aero), then the adoption percentages are different.

We will see more evidence about that later in this blog post. Just note that it’s not only me that has concluded that the FPGA industry is heavily divided on HDL preference.

Web search trends

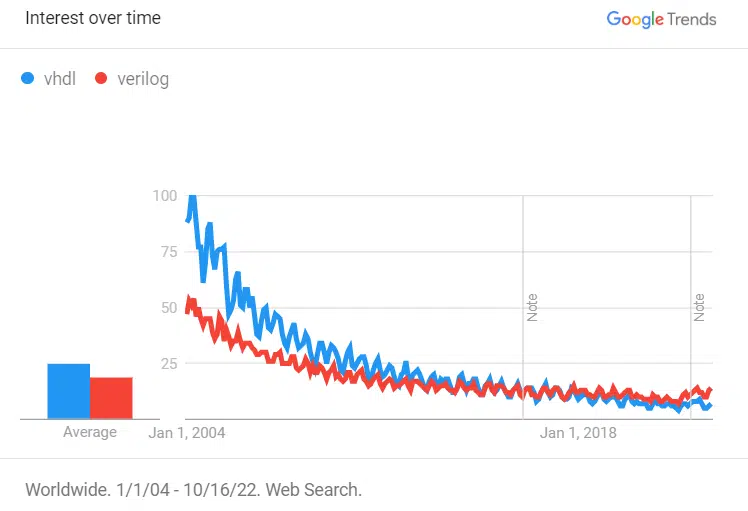

As far as I know, the terms “vhdl” and “verilog” doesn’t have any other meaning than as HDLs. Thus, we can assume that people entering these keywords into Google are looking for information on either VHDL or Verilog.

We can explore this data using the Google Trends tool to get indications of HDL popularity. But remember that Google isn’t the most popular search engine everywhere, and the authorities even block it in some countries. The findings should be more accurate in the Western world.

The chart above shows an accumulation of all the data Google has on the two search terms. The worldwide timeline goes back to 2004 and indicates that VHDL was much more popular many years ago. But in the last few years, the “verilog” search term has overtaken “vhdl”.

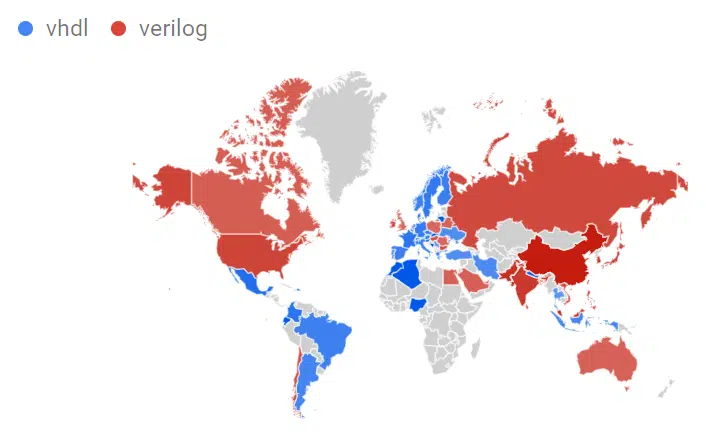

However, the data is heavily skewed among geographical regions. The map above visualizes the VHDL/Verilog web search distribution over the last 12 months (not since 2004, as in the timeline chart).

We can see that VHDL is still dominant in Europe, South America, and most of Southeast Asia, while the US and Canada are leaning towards Verilog. I don’t trust the numbers for China because of internet censorship, so we cannot tell what they prefer.

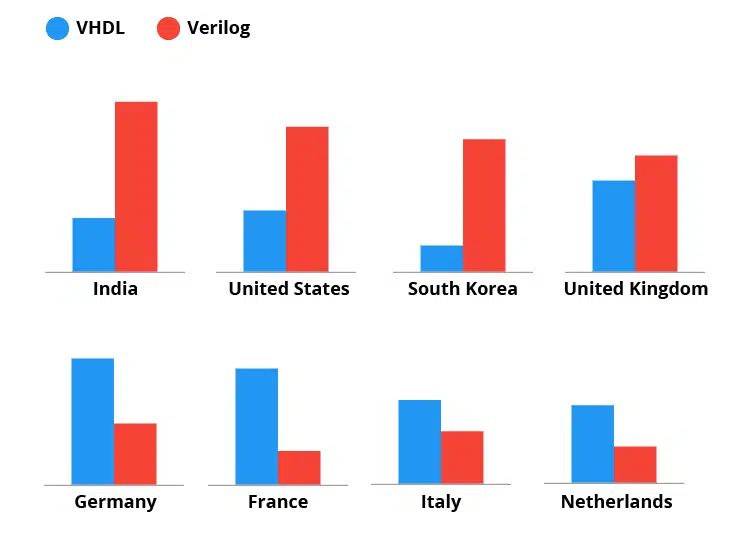

I’ve compiled the chart above that shows the distribution in some major engineering countries, and we can see that the regional differences are significant.

Please note that the units of the graph bars are not percentages, so they don’t add up to 100. Instead, compare the height of the red/blue bars independently for every country to get an impression of which HDL is more prevalent in that region.

VHDLwhiz traffic

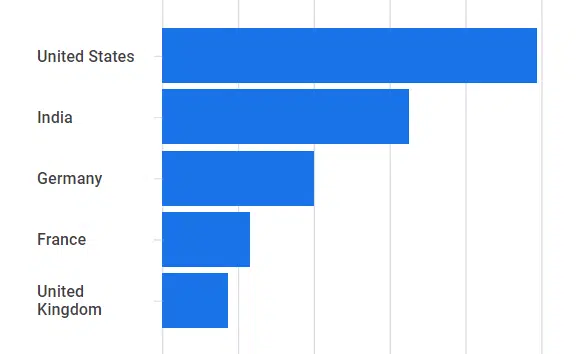

The chart below is from Google Analytics, and it shows the top visiting countries on the VHDLwhiz blog over the last 12 months.

Even though Verilog seems to be more used in the US than VHDL, the United States is still at the top of the visitor list. So we can’t say that VHDL is unpopular in the US; it’s just that Verilog is more used.

Of course, the United States is one large country, while Europe consists of many. If we could compare traffic adjusted for the population number, I suspect European countries would come out on top. Unfortunately, Google Analytics can’t produce such charts.

Academic popularity

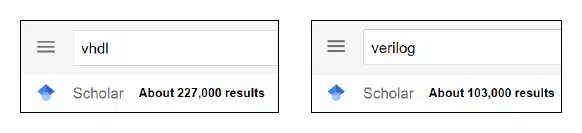

Many say that VHDL is used more in academia than in the industry. Let’s use Google Scholar as a benchmark to find out if that’s true!

After entering, we see that there are more than twice as many academic publications containing the term “vhdl” than “verilog”. While it doesn’t prove anything, it adds to the anecdotal evidence supporting that claim.

Open-source community

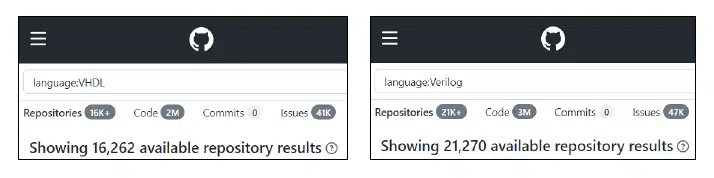

And what does the open-source community use the most? Verilog is the winner on GitHub, with slightly more repositories and code lines.

Note that this also includes all of the major VHDL verification frameworks, which are open-source and on GitHub: OSVVM, UVVM, and VUnit.

Which HDL has more job opportunities?

Should I learn VHDL or Verilog to have the best chance of landing my first FPGA job?

I’m sure many students and FPGA newbies are asking themselves this question, and the answer depends very much on where you are in the world and which industry you are targeting.

Furthermore, it may not be as simple as choosing the HDL with the highest number of job openings either.

VHDL vs. Verilog job openings

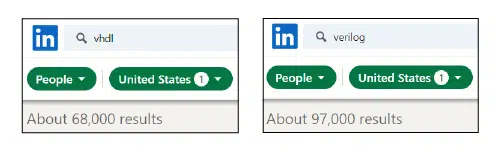

As an experiment, let’s search for US job listings containing the word “vhdl” versus “verilog” on LinkedIn.

As we can see from the screenshots above, there are more Verilog jobs than VHDL jobs. Although, the difference is not as significant as the Google Trends graph suggested.

How many people know VHDL vs. Verilog?

Now, how about if we search for people with VHDL or Verilog skills in the United States?

You can see the search results in the image below. There are also fewer candidates for those VHDL jobs by approximately the same ratio. If you choose Verilog, you will be competing against more people.

How to find out more

I suggest you research companies local to your area or where you wish to move to see what they are using. Usually, it’s easy to find out.

You can find the companies you want to work for on LinkedIn and check out their job openings. If they have none at the moment, you can view the LinkedIn profiles of those who work there to deduce which HDLs the company is using.

But unless your target area and industry are very biased toward one HDL, you can’t really conclude that a particular language will give you more options once you complete the training sometime in the future.

The riches are in the niches

It’s not always best to go with the flow, especially if you want to achieve something other than everyone else. VHDLwhiz and I are living proof of that.

Occasionally, people tell me that I should start writing about Verilog instead because that’s “what everyone is doing” (however, it should be clear now that it’s far from everyone).

I think that would be a big mistake because there are substantially many VHDL users worldwide. Because the tool vendors are trying to sell Verilog, they are not getting the support they need from them, and they come to my website instead.

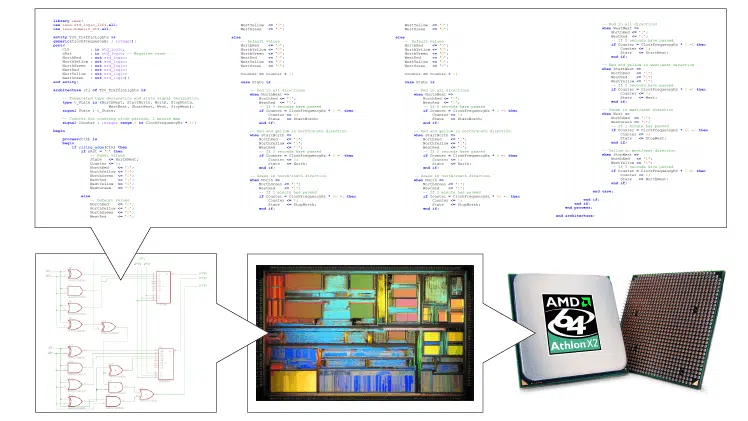

Finally, I want to point out that FPGA design is already a niche industry.

If you wanted to go mainstream, you wouldn’t be reading this text. You would be a web designer like most other IT consultants! So why does the VHDL vs. Verilog question matter that much?

You can make it big in a small market

First of all, VHDL design is not a small market worldwide. But even if it should become less used than Verilog in the future, there would still be enough jobs for skilled VHDL designers.

Some companies will never switch because they are happy with VHDL. Others will still have to deal with it due to decades of legacy projects that need maintenance and new developments.

Think of C++. If you knew it when Java became widespread, would you be unemployed today if you refused to learn Java?

No!

You could have kept going since the early 80s and never been without a job. Even as more modern alternatives like Rust are gaining traction, C++ remains highly relevant.

Likewise, VHDL will not go away even if the worst-case predictions come through, and I don’t think they will.

Top paying languages

How much money you will make as an FPGA engineer depends on many variables, but probably not the HDL you choose to learn. That’s because the popularity of a coding language doesn’t say anything about the salary.

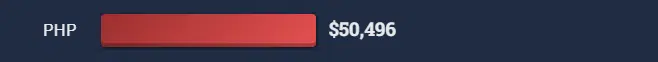

Let’s put this to the test by looking at the Top paying technologies section from Stack Overflow’s Developer Survey. The image below shows the languages at the top of the list.

They are all niche languages, some of which are very old, like LISP and Perl.

Most people have replaced Perl with Python these days, and Python is now the most popular programming language in the world. But Python programmers still make far less on average than Perl monks do.

And look at PHP, the programming language that powers most websites, VHDLwhiz.com included. It’s relatively easy to learn, and there will be jobs in almost any corner of the world. You can see below how much the average PHP programmer earns.

Of course, there are Python and PHP programmers that make lots more. But if we look at the average salary expectations, money is no reason to choose the most popular languages.

The riches are in the niches! 😎

Final thoughts

Nobody can tell you which HDL is best for you because it depends on a set of variables unique to your situation. You have to do some research on your own to find out more.

Things to consider

- Which HDL is prevalent in my region?

- Which industry do I want to work in (or academia)?

- Does my company have a big budget for SystemVerilog simulator licenses?

- Do I want to work with open-source HDL libraries?

- Are there learning resources freely available?

- Is there an open community where I can get support?

And finally, let’s not forget: which language do I like the most?

VHDL learning resources

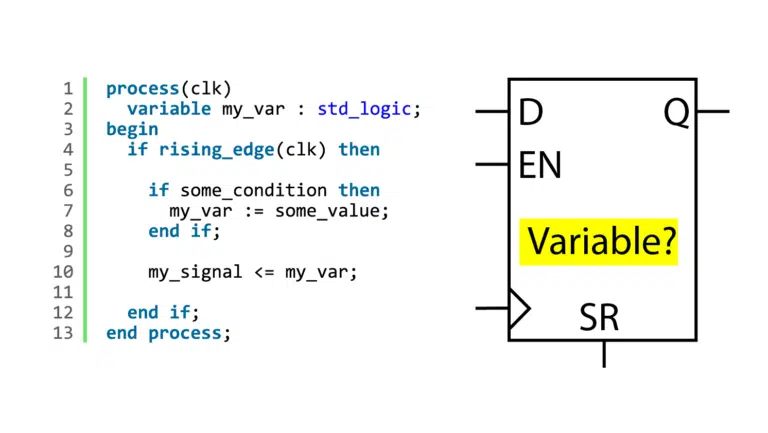

Try my free Basic VHDL Course if you’re new to VHDL. The only thing you need to do this course is a simulator you can install for free.

VHDLwhiz also has a private Facebook group: VHDL for FPGA Engineers, where you can ask questions and chat with the other 10,000+ members and me. It’s free, and you should join today!

Finally, I recommend the VHDLwhiz Membership if you want to learn FPGA design using VHDL beyond the beginner stage. 👇

As a member, you get a new course or resource item every month. And when you join, you can access all the content I’ve previously published in the membership portal.

There are many video tutorials about VHDL and FPGA development waiting for you. But that’s not all. You also get a database of VHDL example projects, templates, code challenges, and quizzes.

Click the banner above to see what’s currently there and join!

There are no hidden fees. You can cancel the monthly renewal at any time.

If one learns VHDL or SystemVerilog first, to learn the other language will be not so difficult as to learn the first one. Both languages allow engineers to achieve the same objective, to design digital hardware. If possible learn both, it will make you a more skilled and versatile engineer, opening a wider ranger of professional opportunities.

Very true! Learning one HDL doesn’t exclude the other. Your understanding of the underlying hardware and digital design principles is transferrable when learning a second language.

Interesting post 🙂

I’m glad you liked it! 🙂

Good post Jonas!

I agree on learning VHDL and Verilog both. I’ve been working with C, Python, bash and VHDL for years.

On the other side, vendors like Xilinx seem not interesting in VHDL and I don’t feel confident in using the VHDL 2008.

In my current job, we work with VHDL, is the trend in Spain and we have a lot of projects in VHDL. It has no sense to migrate everything to Verilog. However, I’m going to start a project as hobby and probably I’ll do it in Verilog. I want to test cocotb, verilator… it seems the open source world, as your post says, is higher.

Fer.

Sure, why not give it a try? It can’t hurt to know both HDLs. Good luck with your hobby project!

Lol, so you’ve decided to open up that can of worms?

I’ll always be VHDL over Verilog. System Verilog should replace Verilog, then it’s game time.

The biggest contributor to Verilogs’s popularity is that it’s easier to teach, so most kids are learning it now. Back in the early 90’s when I got my BSEE, VHDL is what was used in the two classes that used VHDL. (CSE Lab and Intro to VLSI)

The FAA and the US Mil work is usually VHDL (up until recently Verilog started showing up in Mil projects. FAA is still ADA for SW and VHDL for firmware.

Another thing about Verilog, and this is not a good thing, is that there was a shortage of people to write HDL and before HLS a lot of SW guys were coding these early SOC parts like the 7-series Zynq. Some of the most wretched HDL code I’ve ever seen was written for this part. All nested, unreadable if-then-else statements. HDL code bereft of case statements and FSM’s in particular (REM: You design first, top-down and then code bottom-up.)

Verilog also gives you just enough rope to hang yourself. VHDL is more strict and a more strongly typed language. It’s just better than Verilog, hands down. SV vs VHDL is a much better fight. Verilog doesn’t belong in the ring with VHDL.

JMO

Yes, I had to open this can of worms sooner or later. 😅 Thanks for sharing those observations about the history of VHDL and Verilog.

Finally, I think it requires much programming/coding experience to fully understand the benefits of a strongly typed language.

This post makes me very fun. Really nice job!

I like VHDL very much, but I am really disappointed by implementation lack of VHDL-2008 in synthesis tools. So, it is the reason why I have started to learn SystemVerilog to compare support of advanced features.

But, as others have noted, it is just a tool…what is really important is to understand the principles of synthesis and implementation..to see beyond the code 🙂

I think the VHDL users paying for those FPGA tools should demand support for newer VHDL standards. If vendors notice that they are losing customers, they will probably implement support for VHDL-2008 and VHDL-2019.

We who are using the free software versions have nothing to bargain with.

Regarding Xilinx and their VHDL-2008 support (or lack thereof), It’s frustrating that Xilinx seems to have some kind of aversion to VHDL-2008. You can’t make components for Vivado block designs in VHDL-2008 and they have been slow in their support of 2008, (It’s improving, but still no support for BDs). I’m watching closely to see what effect the AMD takeover will have. IMO the synergies (I hate that word and a few others, such as ‘proactive’. I defer to the Simpsons:

https://www.youtube.com/watch?v=PxX7wqW-2v0)

But these synergies, for whatever reason, just didn’t seem to work out as well as expected. I’m hoping things work out better (from my end) for AMD/Xilinx. I’ll be 60 in March and would like to close things out without a major retooling.

Since all of my recent contracts have been predominantly Xilinx projects and I work contracts all over the US, I can share a little experience from my still narrow scope from the US. I have experience with Altera (Intel), Actel(Micro…whatever), and Lattice, but Xilinx seems to be way out in front. The demand for engineers who are proficient with Vivado is in higher demand than Quartus/Qsys (now platform designer) probably due to Vivado being more difficult in so many ways that it’s worthy of a discussion on its own. The 7-series and Ultrascale FPGAs do seem to be favored; however, this might not be true overall, it’s just what I have observed.

The map showing the US favoring Verilog might be directly correlated with it being the HDL of choice for American universities since it’s much easier to learn. (JMO) There’s little debate about Verilog being the easier of the two to learn, butwhether this correlation is valid most certailnly is arguable.

As a HW guy coming out of the RF/analog world in the 80s to early 90s and crossing over to digital, I have no SW bias toward Verilog. VHDL was first because I was working for Raytheon and the military favored VHDL & ADA to C/C++ & Verilog. This was true at the time (the US-Mil created ADA and VHDL was derived from ADA) This may be changing as I’ve run into Verilog working on Blackhawk where the designer for this particular subsystem and a few other guys didn’t know VHDL. Not well enough to code designs, at least. Of course, they hated VHDL but had no choice as the project was adapting to FAA DO254 guidelines for reliability purposes. (A quasi-DO254 because the military is far more interested in the cost, so they have different definitions of what is determined to be a “catastrophic failure”. Let’s leave it at that.) I have never seen a system certified to DO254 DAL-A or DAL-B project coded in Verilog and have never met an FAA-certifying authority who favored Verilog from a reliability perspective.

That’s enough from me, but I’ll close with a quote:

“VHDL contains more constructs for high-level modeling, model parameterization, design reuse, and management of large designs than does Verilog. ”

-Kenneth L. Short

Stony Brook University

It’s always nice to hear from you, Patrick. I think you know more about the backstory of VHDL/Verilog than most of us do.

It shall be interesting to see what AMD will do if anything!

And thanks for the Simpsons gold. 🙂

The 2022 Wilson Verification Survey is out. It is interesting to note that VHDL grew for both design and verification – and they gave up on forecasting.

Maybe you can include the link as the SPAM protection prevented me from doing so.

What I generally recommend to learn first is to do a job search in the area in which you want to live – find a couple of companies that do what you want to do and see what they require.

Thanks, Jim. I’ve updated your comment with the relevant links. And I will try to relax my spam filter.

The new study really does say that VHDL has grown in popularity since 2018, especially for verification. Interesting!

Being a VHDL developer for FPGA designs myself, it is hard to make use of the full feature set of the latest release of VHDL because vendors like Xilinx do not seem one bit interested in supporting that at all. The pinch is felt when working a lot with bus structures, specially AXI-MM, because the interface definitions in VHDL definitions are restricted to a bare minimum with VHDL-200X.

But I do 100% agree with you that VHDL is still the best for design, and with a little more patience, for verification (OSVVM, UVVM).

I think those who are paying for the tool licenses should demand better VHDL support from their sales representative. People like me who only use free versions of the tools have little say in this matter.

Thank you for the article. I’m curious to hear your thoughts on UVM vs. UVVM. Why do you think UVM has gained so much popularity? Which framework do you prefer personally, and which one do you find easier to use and set up?

Looking forward to your insights!

Hello, Anas. I think a big reason is that simulation and implementation tool vendors have promoted Verilog and have been slow to implement VHDL-2019 support. And that’s probably because they make much more money from selling simulator licenses for SystemVerilog features.

I like OVVM, but I find myself using VUnit more often for testbenches.