In the previous tutorial, we learned how to use a For-Loop to iterate over an integer range. But what if we want a more detailed control of the loop than just a fixed integer range? We can use a While-Loop for this.

The While-Loop will continue to iterate over the enclosed code as long as the expression it tests for evaluates to true. Therefore, the While-Loop is suitable for situations where you don’t know exactly how many iterations will be needed in advance.

This blog post is part of the Basic VHDL Tutorials series.

The syntax of the While-Loop is:

while <condition> loop end loop;

The <condition> is a boolean true or false. It can also be an expression that evaluates to true or false. The condition is evaluated before every iteration of the loop, and the loop will continue only if the condition is true.

Example expression which is true if i is less than 10:

i < 10

Example expression which is true if i is not 10:

i /= 10

Example expression which is true if i is greater than or equal to 0, and less than 28=256:

i >= 0 and i < 2**8;

Relational operators:

| = | equal |

| /= | not equal |

| < | less than |

| <= | less than or equal |

| > | greater than |

| >= | greater than or equal |

Logical operators:

| not a | true if a is false |

| a and b | true if a and b are true |

| a or b | true if a or b are true |

| a nand b | true if a or b is false |

| a nor b | true if a and b are false |

| a xor b | true if exactly one of a or b are true |

| a xnor b | true if a and b are equal |

Exercise

In this video tutorial, we learn to use a variable to control a While-Loop:

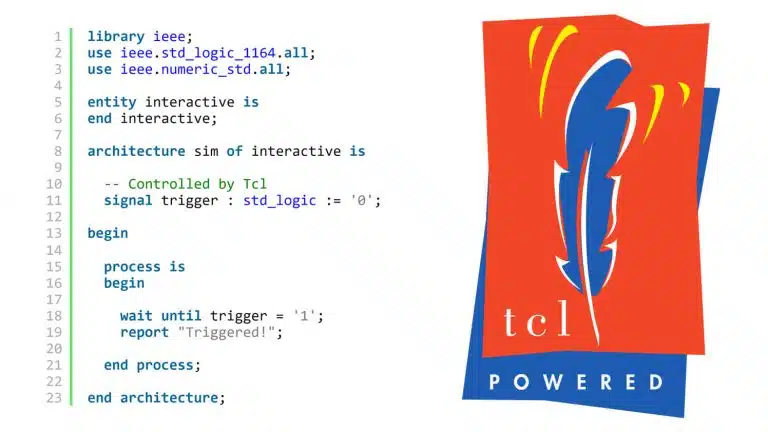

The final code we created in this tutorial:

entity T05_WhileLoopTb is

end entity;

architecture sim of T05_WhileLoopTb is

begin

process is

variable i : integer := 0;

begin

while i < 10 loop

report "i=" & integer'image(i);

i := i + 2;

end loop;

wait;

end process;

end architecture;

The output to the simulator console when we pressed the run button in ModelSim:

VSIM 2> run # ** Note: i=0 # Time: 0 ns Iteration: 0 Instance: /t05_whilelooptb # ** Note: i=2 # Time: 0 ns Iteration: 0 Instance: /t05_whilelooptb # ** Note: i=4 # Time: 0 ns Iteration: 0 Instance: /t05_whilelooptb # ** Note: i=6 # Time: 0 ns Iteration: 0 Instance: /t05_whilelooptb # ** Note: i=8 # Time: 0 ns Iteration: 0 Instance: /t05_whilelooptb

Analysis

We created an integer variable i and gave it an initial value of 0. We used an expression in the While-Loop that is true as long as i is less than 10. Because we were incrementing i by 2 in each iteration, the last number that was printed out was 8.

On the next iteration, the i < 10 evaluated to false because 10 is not less than 10. After the loop terminated, the program hit the wait; where it paused infinitely.

Get free access to the Basic VHDL Course

Download the course material and get started.

You will receive a Zip with exercises for the 23 video lessons as VHDL files where you fill in the blanks, code answers, and a link to the course.

By submitting, you consent to receive marketing emails from VHDLwhiz (unsubscribe anytime).

Takeaway

- The While-loop will continue as long as the condition is

true - The condition is evaluated before every iteration of the While-Loop

- Variables may be declared and used within a process

Take the Basic VHDL Quiz – part 1 »

or

Go to the next tutorial »

Why is variable declaration not needed for For loop and only for while loop?

That’s because there’s an implicit variable name you can use within the loop.

Here, you can use

valin the loop like a variable.Actually, it’s more like a constant in the VHDL For loop because you can’t change its value from within the For loop like you can in most programming languages. If you need that, go for a While loop.