I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to create a clocked process in VHDL

The vast majority of VHDL designs uses clocked logic, also known as synchronous logic or sequential logic. A clocked process is triggered only by a master clock signal, not when any of the other input signals change. The basic building block of clocked logic is a component called the flip-flop. There are different variants of…

How to use Signed and Unsigned in VHDL

The signed and unsigned types in VHDL are bit vectors, just like the std_logic_vector type. The difference is that while the std_logic_vector is great for implementing data buses, it’s useless for performing arithmetic operations. If you try to add any number to a std_logic_vector type, ModelSim will produce the compilation error: No feasible entries for…

How to use a While loop in VHDL

In the previous tutorial, we learned how to use a For-Loop to iterate over an integer range. But what if we want a more detailed control of the loop than just a fixed integer range? We can use a While-Loop for this. The While-Loop will continue to iterate over the enclosed code as long as…

Basic VHDL quiz – Part 4

Test your progress with this VHDL quiz after completing part 4 of the Basic VHDL Tutorial series!

How to use an impure function in VHDL

An impure function can read or write any signal within its scope, also those that are not on the parameter list. We say that the function has side effects. What we mean by “side effects” is that it is not guaranteed that the function will return the same value every time it is called with…

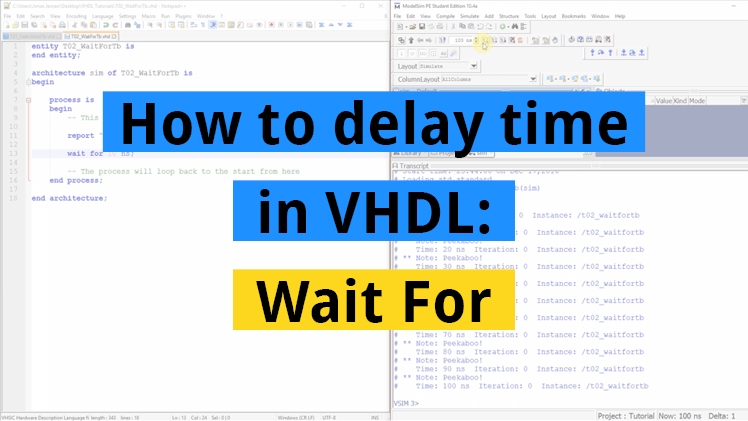

How to delay time in VHDL: Wait For

In the previous tutorial we learned that a process can be thought of as a program thread. We also learned that a wait; statement causes the program to pause indefinitely. But is there a way to make a program wait for any other time value than forever? If we remove the wait; altogether and try…

Dear Jonas

Thanks for the content, thumbs up. please keep up the good work!

Best Regards

Thanks! That’s good to hear.

You are doing a very nice job. Top quality!

Thanks! I really appreciate your comment.

Hello Jonas

You really did save me by these great videos and materials.

These tutorials are the best thing on the internet.

Thank you for creating them.

Thanks! That’s encouraging to hear. I will do my best to keep up the quality of my blog posts.

Thank you so much man you are awesome! i learnt vhdl in university but i forgot after all years. i started again working. You help me too much! i will continue to course after this beginner course. i am planning the begin beginner fast track ! please dont stop the teaching us . thank you so much! greetings from turkey 🙂

Hello, Utku. Thank you for the nice comment! I’m glad you found my blog to be helpful. I will keep the free and premium content coming your way.

Thank you for providing such great content on a subject that imo can be tricky to really understand. But you make it easy for everyone!

That’s great to hear! I will keep on creating tutorials and articles for you. ?

Dear Jonas,

I’m an electronic engineer from Morocco, currently studying for a masters degree in microelectronics and sensors in France.

You helped me a lot to remember some of the vhdl basics and get more further into it.

I worked on an academic project using basys3 and vivado for a vga controller.

Thank you very much for this great content, keep up the good work.

I’m glad you like the quiz. It’s a good way to refresh your knowledge. 🙂

Excellent learning tool

Thanks! By the way, I also use quizzes in the VHDLwhiz membership.

Great tutorials! Short and sweet!

I’ll be sure to go onto the FPGA and VHDL Fast-Track after completing the basic tutorials..

Thanks, Dale! Also, check out the VHDLwhiz Membership, which gives you multiple courses, resource items, and coding challenges and supports your success in FPGA design.

Nice quiz, only problem is sharing your score on facebook is not working.

Thanks for the feedback. I’ve created a task on this. I’ll see if I can fix it when I have the time.