I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use an impure function in VHDL

An impure function can read or write any signal within its scope, also those that are not on the parameter list. We say that the function has side effects. What we mean by “side effects” is that it is not guaranteed that the function will return the same value every time it is called with…

Formal verification in VHDL using PSL

When designing VHDL for safety-critical FPGA applications, it’s not enough to write testbenches at best-effort. You have to present proof that the module works as intended and without undesirable side-effects. Formal verification techniques can help you map a requirement to a test, proving that your VHDL module conforms to the specification. It’s an instrumental tool…

How to use Signed and Unsigned in VHDL

The signed and unsigned types in VHDL are bit vectors, just like the std_logic_vector type. The difference is that while the std_logic_vector is great for implementing data buses, it’s useless for performing arithmetic operations. If you try to add any number to a std_logic_vector type, ModelSim will produce the compilation error: No feasible entries for…

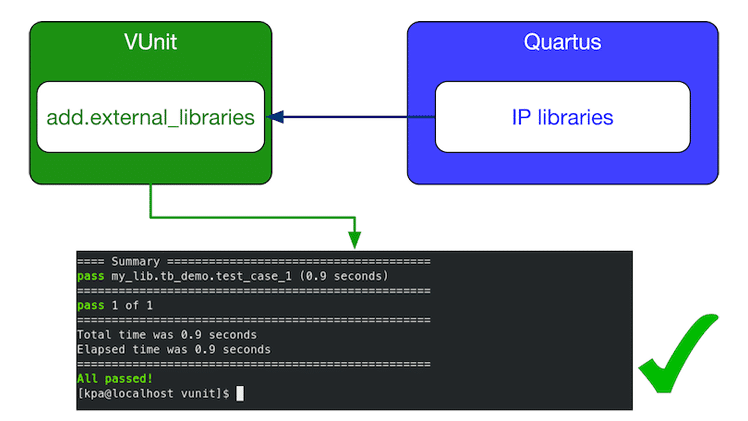

How to link Quartus Prime IP libraries to VUnit

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework?

This tutorial shows you how to generate, incorporate, and link external Quartus IP libraries to VUnit.

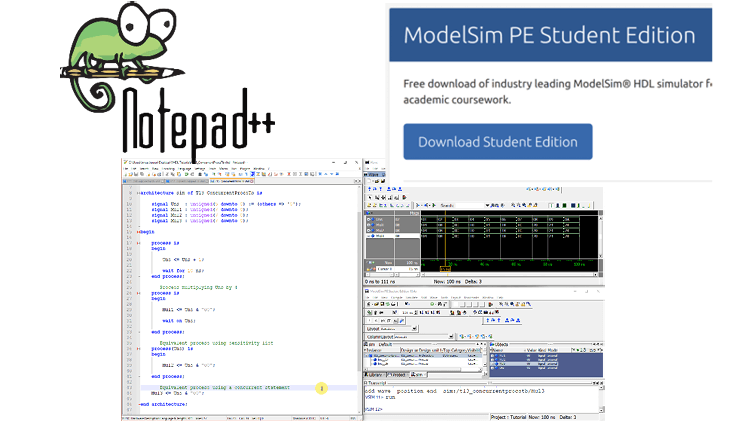

How to install a VHDL simulator and editor for free

Although VHDL and FPGA tools are often very expensive, it is easy to access state-of-the-art software for free if you are a student. There are several simulators, editors, and IDEs for working with VHDL. This article shows you how to install two of the most popular programs used by VHDL engineers. VHDL simulator Siemens EDA’s…

How a signal is different from a variable in VHDL

In the previous tutorial we learned how to declare a variable in a process. Variables are good for creating algorithms within a process, but they are not accessible to the outside world. If a scope of a variable is only within a single process, how can it interact with any other logic? The solution for…