Course: Protected type string list

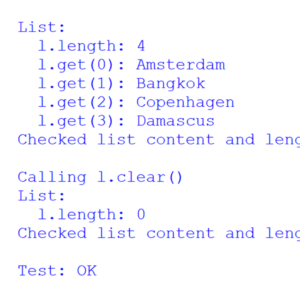

Learn to create a dynamic string list in VHDL based on Python’s list class. Use a protected type to store any number of strings of any length during simulation.

These are the paid/premium products in the VHDLwhiz shop.

Showing 25–35 of 35 results

Learn to create a dynamic string list in VHDL based on Python’s list class. Use a protected type to store any number of strings of any length during simulation.

Understanding how delta cycles work in VHDL is key to becoming proficient in FPGA design. This course teaches you how signal scheduling works in simulation.

Learn to convert a Lattice iCEcube2 GUI project into a Makefile-based workflow. Manage your FPGA implementation project entirely from the command line.

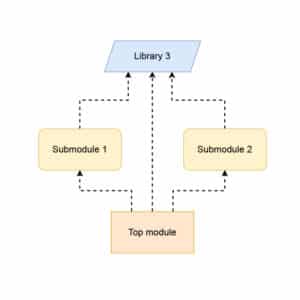

Learn how to structure a VHDL project with multiple submodules. Use scripts to derive the compile order, launch simulations, and run regression tests.

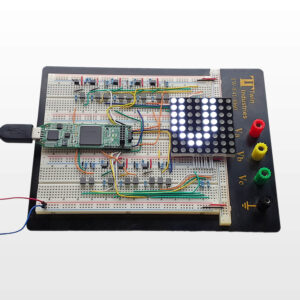

Learn how to create a VHDL project from scratch with self-checking testbenches. Dot Matrix is the most extensive course VHDLwhiz has ever made.

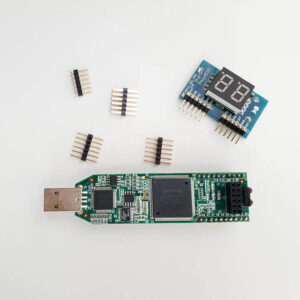

Hands-On for Absolute Beginners. Understand the basics of FPGA development using VHDL in a few evenings!

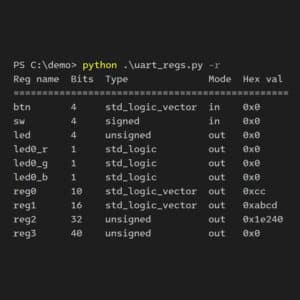

This tool generates a VHDL module and a Python script to read from or write to any number of custom FPGA registers using UART.

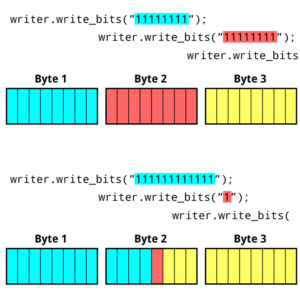

These VHDL packages provide a user-friendly interface for binary file access in simulation to read or write bit vectors of any length.

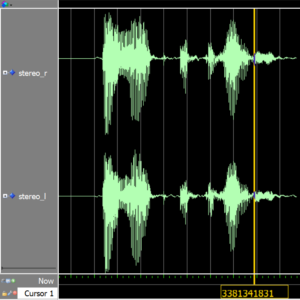

These VHDL packages read and write WAV audio files. They provide a user-friendly way to run VHDL simulations on audio processing modules.

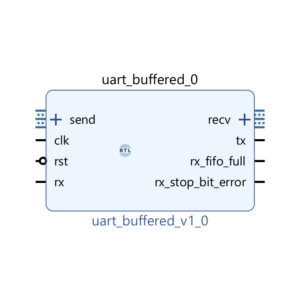

This project contains three general-purpose, AXI compatible, universal asynchronous receiver-transmitter (UART) modules.

This VHDL package can store any data type in dynamic memory. It mimics the behavior of Python’s list class and supports negative indexing.

End of content

End of content