In short, VHDL is a computer language used for designing digital circuits.

I use the term “computer language” to distinguish VHDL from other, more common programming languages like Java or C++. But is VHDL a programming language? Yes, it is. It’s a programming language that is of no use when it comes to creating computer programs!

VHDL is an event-driven, parallel programming language. While it isn’t suitable for creating programs that can be run by a CPU on a computer, it’s great for creating the actual CPU. It’s a Hardware Description Language, which means that it can be used for designing digital logic.

Access the Basic VHDL Tutorials series here!

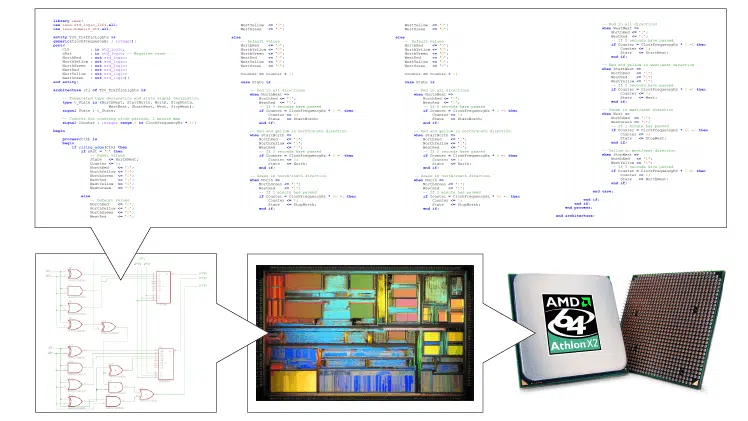

Consider the above illustration. Inside the CPU chip, there are lots and lots of mostly digital electronic circuits (middle). These digital circuits can be shown using a schematic diagram (right). When creating an integrated circuit chip, like the CPU, we have to start by creating the logical circuit diagram to the right.

It’s a fair assumption that such circuit diagrams are created in some kind of schematic editor, but this isn’t how it’s done. The circuits are described in a textual language like VHDL.

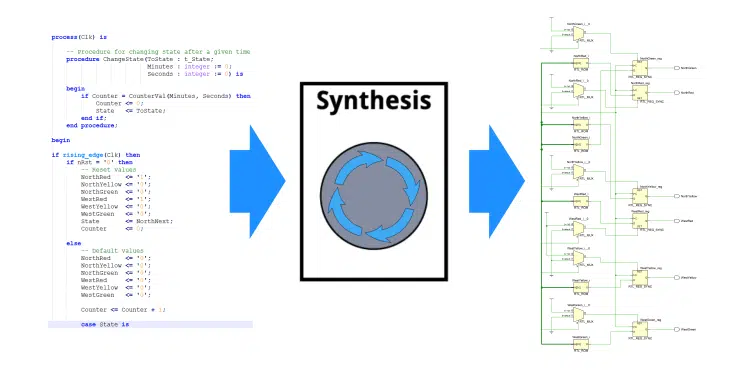

Synthesis

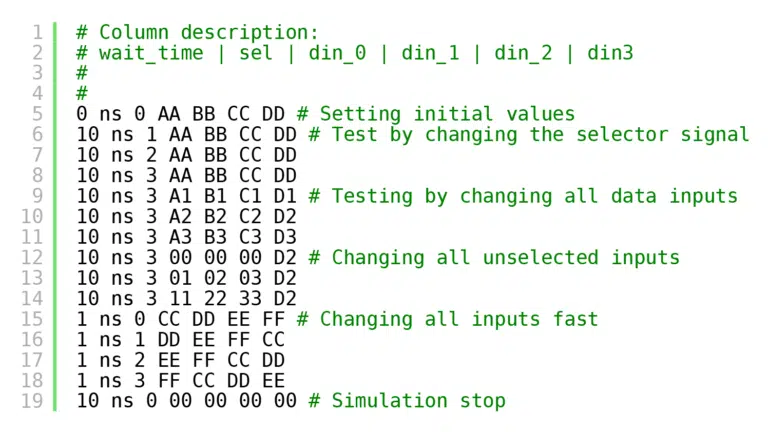

Instead of drawing the exact circuits in a schematic editor, we use VHDL to describe the desired behavior of the circuit. The VHDL code can then be converted into an exact schematic in a process called synthesis. The synthesis tool is a software application that takes the VHDL code and tries to find a possible solution to the behavior you have described.

If successful, the output from the synthesizer will be a netlist, which can be viewed in a schematic editor.

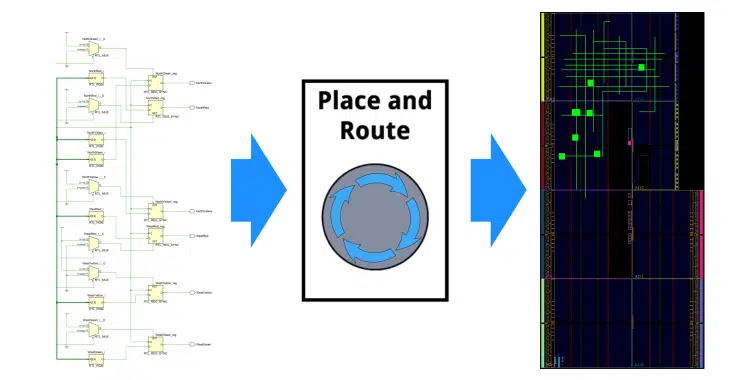

Place and Route

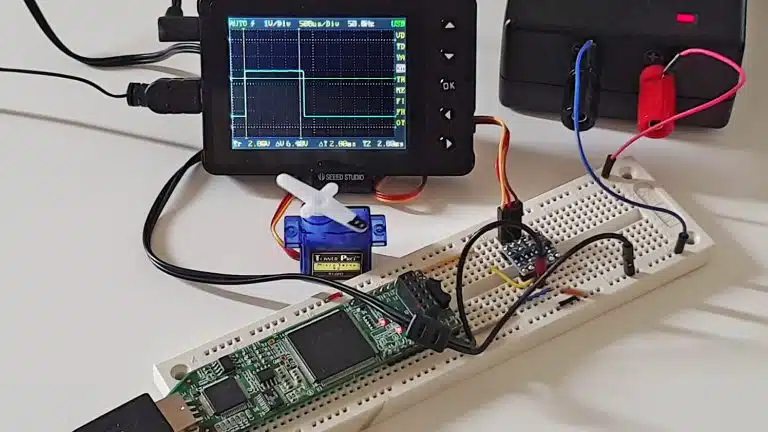

While the netlist gives an exact logical description of the circuit, it doesn’t say anything about the physical implementation. To derive a precise description of the physical layout, the netlist is run through a process called place and route, or PAR for short. The router will try to allocate the elements from the netlist to physical components on the target device. It also needs to route wires between all the components. It’s a giant puzzle that the router has to solve!

If successful, the output from PAR will be another kind of netlist. This netlist contains placement and routing info and is specific for the target device type. If the target device is an FPGA, the routed netlist can be converted into a programming file. If the target device is an ASIC, things will be a bit more complicated.

So, What is VHDL?

It’s a sort of programming language which is used for creating digital logic for integrated circuits.

I think that calling VHDL a “programming language” is not good for the reasons you have stated. “computer language” is better, but I think still misses the point. I suggest that it might be better to describe it as a “digital logic system description, design and simulation language” that syntactically resembles some programming language constructs. (This same description would also apply to Verilog).

I suggest that using the term “code” when referring to VHDL constructs is also perhaps not a good idea.

It’s hard to come up with a term that’s easy to understand and describes VHDL accurately at the same time.

Thank you for commenting!

Hi Jonas,

I have recently been learning VHDL using your tutorials and I must say that they are put together and presented so well for beginners. In particular, I like the early introduction of simulation and the use of test benches to present the basics of VHDL. Also the tutorials progress in a well thought out order making it a pleasure to follow.

Many thanks for your efforts and willingness to pass on your expert knowledge of the subject.

Regards

Dave Jones

Thank you, Dave. I really appreciate your nice comment. Use the free resources as much as you like. 😊