I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use the most common VHDL type: std_logic

The most common type used in VHDL is the std_logic. Think of this type as a single bit, the digital information carried by a single physical wire. The std_logic gives us a more fine-grained control over the resources in our design than the integer type, which we have been using in the previous tutorials. Normally,…

How to use Loop and Exit in VHDL

In the previous tutorial we learned how to delay time using the wait for statement. We also learned about the process loop. We now know that if we let it, the process “thread” will loop within the process forever. But what if we want to do something just once at the beginning of the process?…

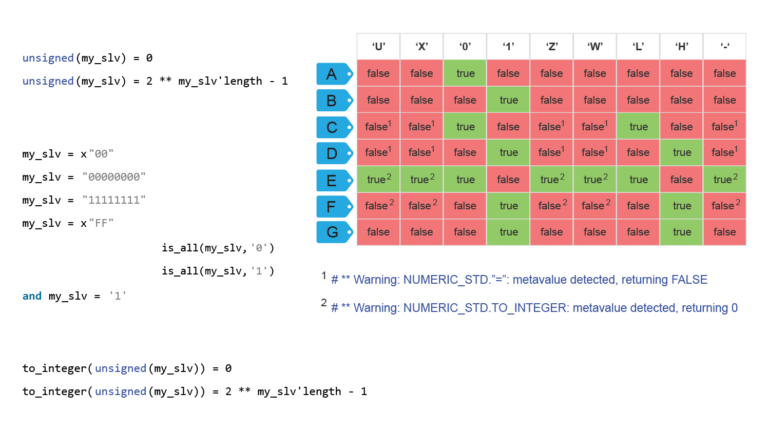

How to check if a vector is all zeros or ones

I know that I have googled this at least a hundred times throughout my career as an FPGA engineer; how to check if all bits in a std_logic_vector signal are ‘0’ or ‘1’. Of course, you know a few ways to do it already, but you want to find the most elegant code that will…

Basic VHDL quiz – Part 1

Put your skills to the test with this quiz with questions from the first part of the Basic VHDL Tutorial series.

An Introduction to FPGAs & Programmable Logic

This video is an introductory presentation about FPGA and programmable logic technology. I delivered this 45 minutes talk at an event hosted by 7 Peaks Software in Bangkok, Thailand, on November 19th, 2019.

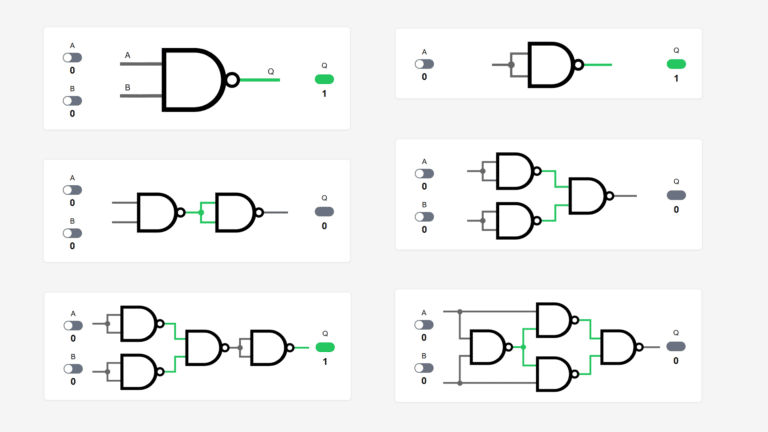

NAND logic gates interactive demo

We can construct any other digital logic gate using only NAND gates as building blocks. This is why NAND is known as a universal gate. NAND logic is widely used as the foundation for designing digital circuits in modern integrated chips. Actually, NOR is also a universal gate, but NAND logic is more prevalent than…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.