I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

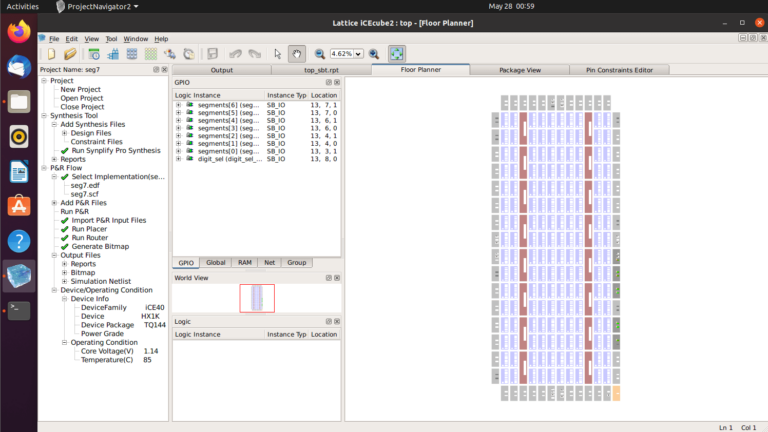

Make Lattice iCEcube2 work on Ubuntu 20.04 and program the iCEstick FPGA board

This tutorial shows how to install the Lattice iCEcube2 FPGA design software on Ubuntu 20.04. Instead of the Lattice Diamond Programmer, we will use the alternative programmer from Project IceStorm that works flawlessly on Ubuntu Linux. The Lattice iCEcube2 FPGA design software only works on Red Hat-based Linux distributions out of the box. Fortunately, we…

How to use Wait On and Wait Until in VHDL

In the previous tutorial we learned the main differences between signals and variables. We learned that signals have a broader scope than variables, which are only accessible within one process. So how can we use signals for communication between several processes? We have already learned to use wait; to wait infinitely, and wait for to…

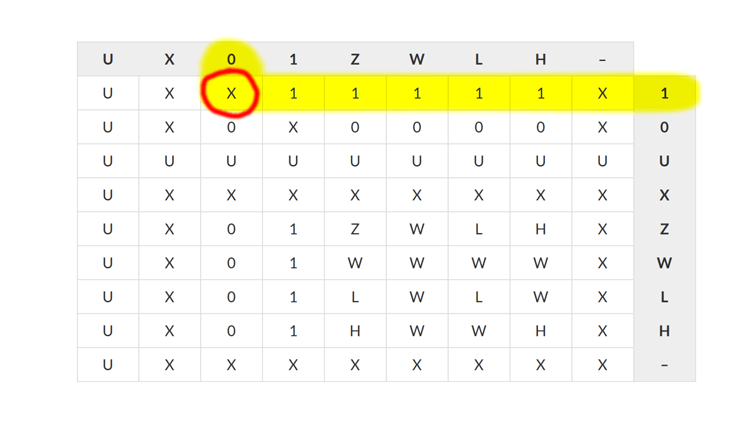

std_logic vs std_ulogic

VHDL includes few built-in types but offers several additional types through extension packages. Two of the most widely used types are std_logic and std_ulogic. The difference between them is that the former is resolved while the latter isn’t. Before we go on to investigate what it means that a type is resolved, let’s first look…

How to create a process with a sensitivity list in VHDL

You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed. We’ve already learned to use the…

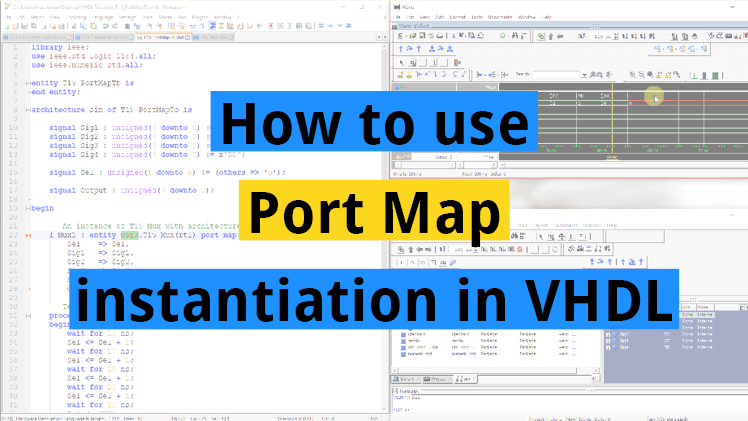

How to use Port Map instantiation in VHDL

A module is a self-contained unit of VHDL code. Modules communicate with the outside world through the entity. Port map is the part of the module instantiation where you declare which local signals the module’s inputs and outputs shall be connected to. In previous tutorials in this series we have been writing all our code…

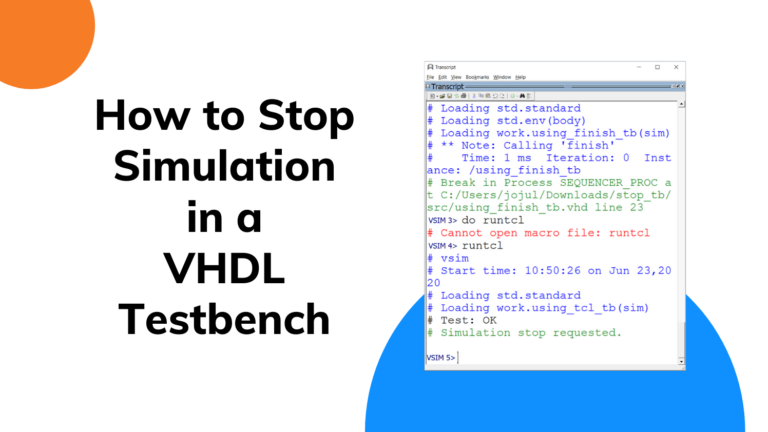

How to stop simulation in a VHDL testbench

How do you stop the VHDL simulator when the simulation is complete? There are several ways to do that. In this article, we will examine the most common ways to end a successful testbench run. The VHDL code presented here is universal, and it should work in any capable VHDL simulator. For the methods involving…

Dear Jonas

Thanks for the content, thumbs up. please keep up the good work!

Best Regards

Thanks! That’s good to hear.

You are doing a very nice job. Top quality!

Thanks! I really appreciate your comment.

Hello Jonas

You really did save me by these great videos and materials.

These tutorials are the best thing on the internet.

Thank you for creating them.

Thanks! That’s encouraging to hear. I will do my best to keep up the quality of my blog posts.

Thank you so much man you are awesome! i learnt vhdl in university but i forgot after all years. i started again working. You help me too much! i will continue to course after this beginner course. i am planning the begin beginner fast track ! please dont stop the teaching us . thank you so much! greetings from turkey 🙂

Hello, Utku. Thank you for the nice comment! I’m glad you found my blog to be helpful. I will keep the free and premium content coming your way.

Thank you for providing such great content on a subject that imo can be tricky to really understand. But you make it easy for everyone!

That’s great to hear! I will keep on creating tutorials and articles for you. ?

Dear Jonas,

I’m an electronic engineer from Morocco, currently studying for a masters degree in microelectronics and sensors in France.

You helped me a lot to remember some of the vhdl basics and get more further into it.

I worked on an academic project using basys3 and vivado for a vga controller.

Thank you very much for this great content, keep up the good work.

I’m glad you like the quiz. It’s a good way to refresh your knowledge. 🙂

Excellent learning tool

Thanks! By the way, I also use quizzes in the VHDLwhiz membership.

Great tutorials! Short and sweet!

I’ll be sure to go onto the FPGA and VHDL Fast-Track after completing the basic tutorials..

Thanks, Dale! Also, check out the VHDLwhiz Membership, which gives you multiple courses, resource items, and coding challenges and supports your success in FPGA design.

Nice quiz, only problem is sharing your score on facebook is not working.

Thanks for the feedback. I’ve created a task on this. I’ll see if I can fix it when I have the time.