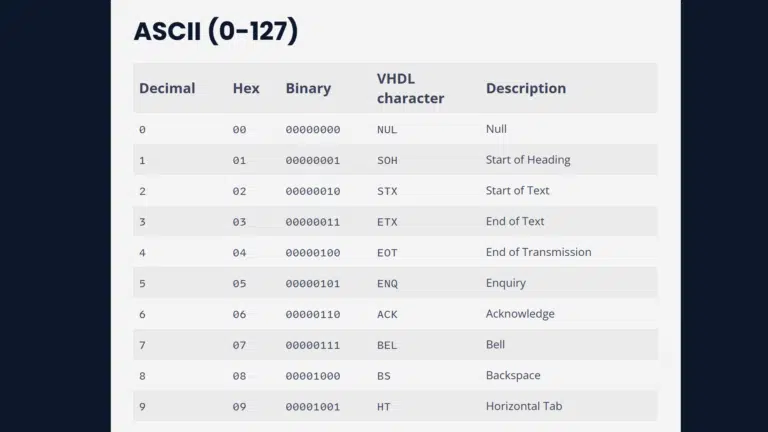

ASCII table

VHDL has a built-in character type that can represent ASCII and Latin-1 characters. It’s in the standard (STD) library, which is loaded by default. You don’t need to import it. Below, you can find the character type definition from the Language Reference Manual (LRM) and tables that list and explain all 256 values. ASCII (0-127)…