I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

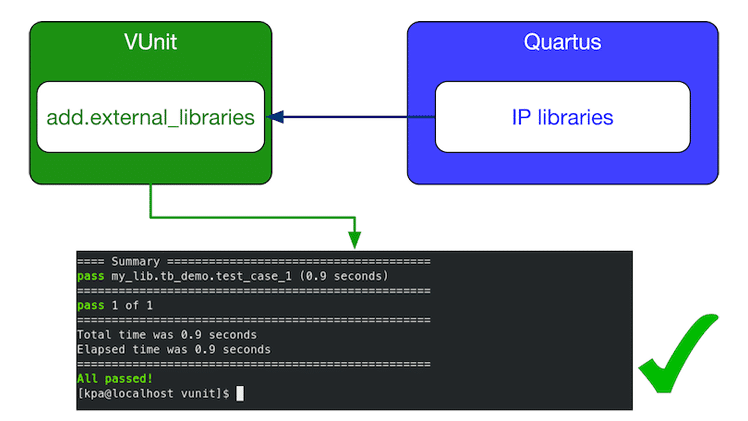

How to link Quartus Prime IP libraries to VUnit

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework?

This tutorial shows you how to generate, incorporate, and link external Quartus IP libraries to VUnit.

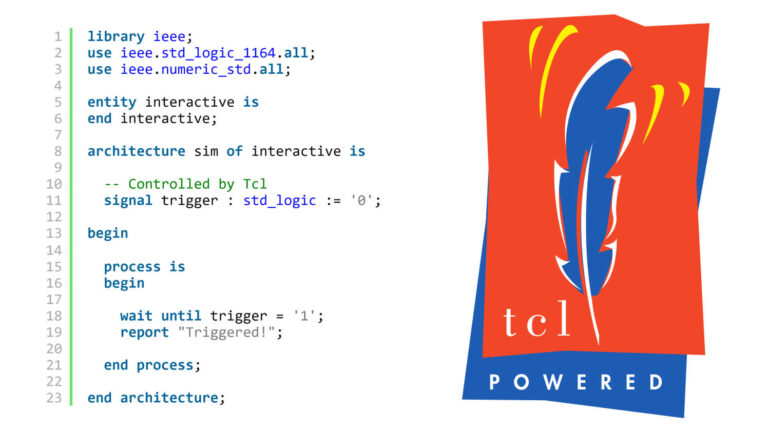

Interactive testbench using Tcl

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you should always create a self-checking testbench, an interactive testbench can…

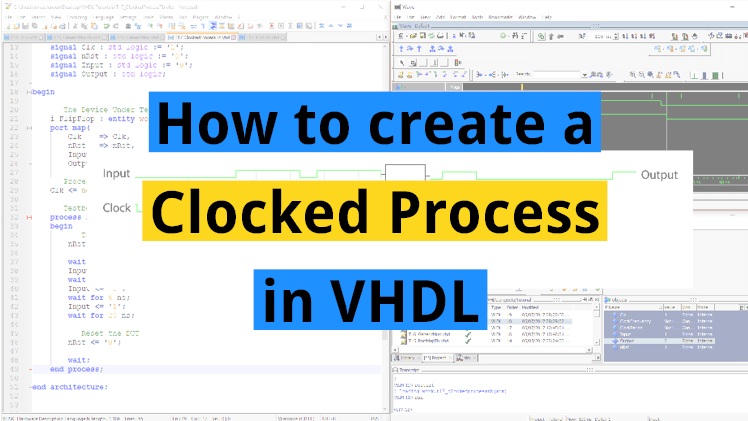

How to create a clocked process in VHDL

The vast majority of VHDL designs uses clocked logic, also known as synchronous logic or sequential logic. A clocked process is triggered only by a master clock signal, not when any of the other input signals change. The basic building block of clocked logic is a component called the flip-flop. There are different variants of…

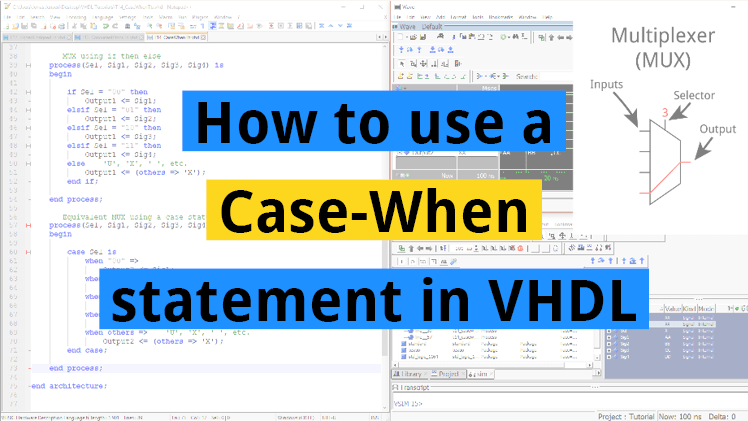

How to use a Case-When statement in VHDL

The Case-When statement will cause the program to take one out of multiple different paths, depending on the value of a signal, variable, or expression. It’s a more elegant alternative to an If-Then-Elsif-Else statement with multiple Elsif’s. Other programming languages have similar constructs, using keywords such as a switch, case, or select. Among other things,…

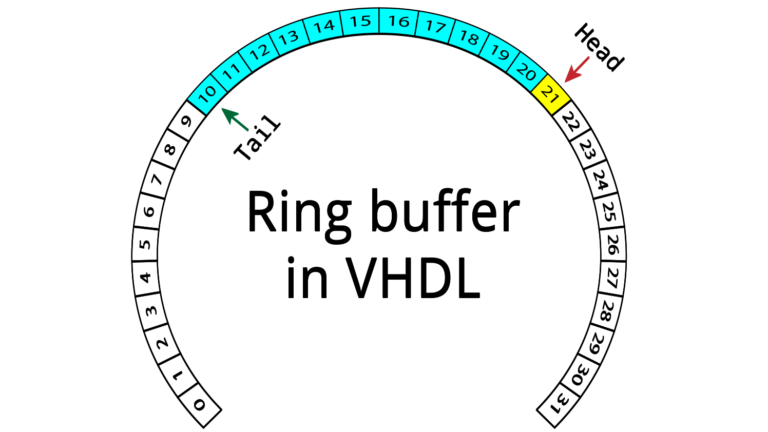

How to create a ring buffer FIFO in VHDL

Circular buffers are popular constructs for creating queues in sequential programming languages, but they can also be implemented in hardware. In this article, we will create a ring buffer in VHDL to implement a FIFO in block RAM. There are many design decisions you will have to make when implementing a FIFO. What kind of…

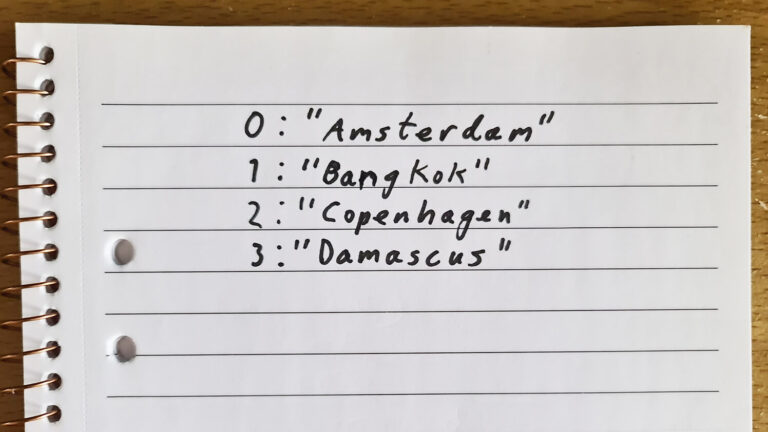

How to create a list of strings in VHDL

Text strings in VHDL are generally limited to fixed-length character arrays. That makes sense because VHDL describes hardware, and generic-length strings require dynamic memory. To define an array of strings, you have to allocate space at compile-time for the highest number of strings you want to store. And even worse, you must decide on the…