You should always use a sensitivity list to trigger processes in production modules. Sensitivity lists are parameters to a process which lists all the signals that the process is sensitive to. If any of the signals change, the process will wake up, and the code within it is executed.

We’ve already learned to use the wait on and wait until statements for waking up a process when a signal changes. However, to be honest, this isn’t how I write most of my processes.

This blog post is part of the Basic VHDL Tutorials series.

When writing VHDL code, the style of writing depends on whether or not the code is intended to be run only in a simulator. If I’m writing simulation code, like we have been doing in this tutorial series, I always use wait statements to control the processes. If I’m writing code that I intend to create a physical implementation of, I never use wait statements.

The syntax for a process with a sensitivity list is:

process(<signal1>, <signal2>, ..) is

begin

<main logic here>

end process;

An important quirk with the sensitivity list is that all signals that are read within the process must be on the sensitivity list. However, the simulator won’t inform you if you fail to add a signal to the sensitivity list, because it’s legal in the VHDL language. The problem is that if you fail to do this, the code will behave differently when synthesized and used in a physical implementation.

In VHDL-2008, the keyword all is allowed to use instead of listing every signal. Unfortunately, most synthesizing software don’t support this newer revision of the VHDL language.

Exercise

In this video tutorial we will learn how to create a process using a sensitivity list in VHDL:

The final code we created in this tutorial:

entity T09_SensitivityListTb is

end entity;

architecture sim of T09_SensitivityListTb is

signal CountUp : integer := 0;

signal CountDown : integer := 10;

begin

process is

begin

CountUp <= CountUp + 1;

CountDown <= CountDown - 1;

wait for 10 ns;

end process;

-- Process triggered using Wait On

process is

begin

if CountUp = CountDown then

report "Process A: Jackpot!";

end if;

wait on CountUp, CountDown;

end process;

-- Equivalent process using a sensitivity list

process(CountUp, CountDown) is

begin

if CountUp = CountDown then

report "Process B: Jackpot!";

end if;

end process;

end architecture;

The output to the simulator console when we pressed the run button in ModelSim:

VSIM 2> run # ** Note: Process A: Jackpot # Time: 40 ns Iteration: 1 Instance: /t09_sensitivitylisttb # ** Note: Process B: Jackpot # Time: 40 ns Iteration: 1 Instance: /t09_sensitivitylisttb

Analysis

We can see from the printouts that the two processes behave alike. That is because a process with a sensitivity list is by definition equivalent to a process with wait on at the end of the process.

Processes with sensitivity lists are normally used in code that is intended to be synthesized. Such code is commonly referred to as register-transfer level (RTL) code. This is a convention, but there are good reasons for it. Although some wait on and wait until statements can be synthesized, it’s hard to know what kind of hardware it will create.

Get free access to the Basic VHDL Course

Download the course material and get started.

You will receive a Zip with exercises for the 23 video lessons as VHDL files where you fill in the blanks, code answers, and a link to the course.

By submitting, you consent to receive marketing emails from VHDLwhiz (unsubscribe anytime).

Takeaway

- A process with a sensitivity list is equivalent to a process with

wait onat the end - All signals that are being read within a process must be on the sensitivity list

- Use

waitstatements in simulation code, and sensitivity lists in RTL code

Hi! I can`t understand what is a difference between that “wait on…” placed at the end of process, and at the begining of process…

The difference is what happens when the simulation starts.

If you place the WAIT ON at the beginning of the process, what comes after only runs when one of the listed signals (wait on sig1, sig2;) changes.

But if you place WAIT ON at the end of the process, the logic above it is evaluated immediately when the simulation begins, in the first delta cycle.

If you are trying to describe logic in the FPGA, you have to use the latter type because when the FPGA is powered up, the combinational paths in the device will not wait but update their outputs to follow the inputs immediately.

You can place the WAIT ON at the beginning in testbenches and simulation code if that’s practical for you.

A process with a sensitivity list is equivalent to a process with wait on at the end

Why so?

It’s just the way VHDL works. Here’s the exact wording from the VHDL language reference manual:

If a process sensitivity list appears following the reserved word process, then the process statement is assumed to contain an implicit wait statement as the last statement of the process statement part; this implicit wait statement is of the form:

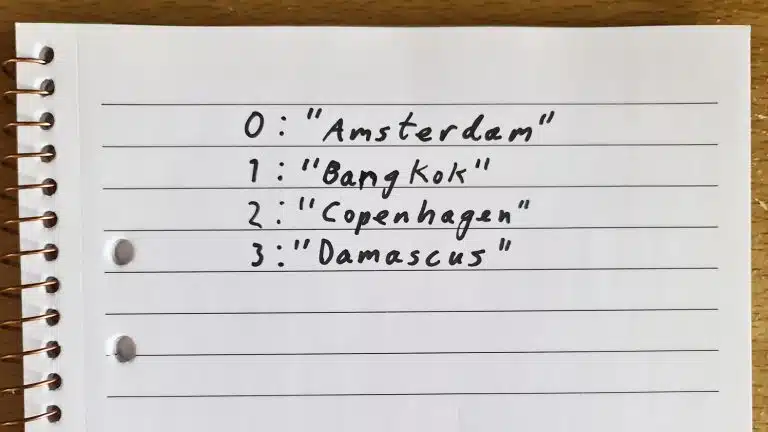

Thus, these are equivalent:

It’s normal to use the process() form in RTL modules and the wait on notation in simulation modules. It’s like a convention, but you can use them interchangeably.