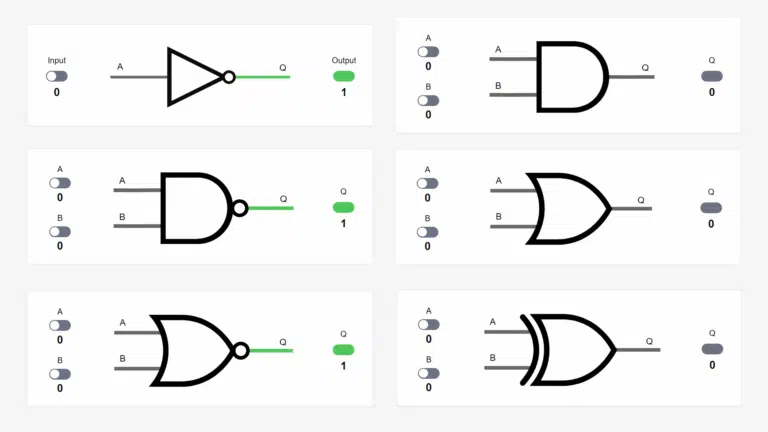

Logic gates interactive demo

The basic logic gates NOT, AND, NAND, OR, NOR, XOR, and XNOR are fundamental building blocks in digital circuits corresponding to Boolean operators.

Play with the switches to see how the outputs change! 😀

The basic logic gates NOT, AND, NAND, OR, NOR, XOR, and XNOR are fundamental building blocks in digital circuits corresponding to Boolean operators.

Play with the switches to see how the outputs change! 😀

Have fun and learn from this VHDL and FPGA design quiz with 28 questions for beginners and intermediate learners in random order.

All questions include an explanation for the correct answer that will be shown after you make your selection.

Which HDL is the most popular, and should I learn VHDL or Verilog? That’s a question I often get asked, and it’s understandable. People want to future-proof their learning by betting on the winning horse. But which one is it, and does it matter?

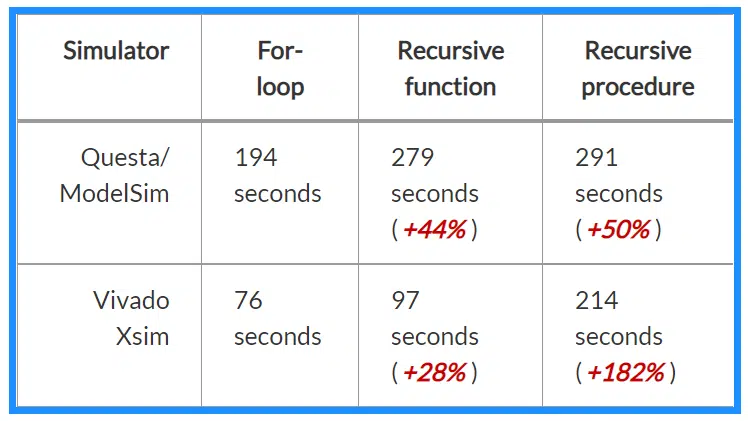

There are controversies in the VHDL community about how you can and shouldn’t use subprograms. Some say you should avoid using functions or procedures in synthesizable (RTL) code. While there are debatable subjective reasons to restrict the use of subprograms, many of these beliefs stem from myths or misconceptions. Therefore, I’m writing this article to…

The ready/valid hardware data transfer protocol is simple and ingenious, providing flow control with only two control signals. The rules are straightforward: data transfer only happens when both ready and valid are ‘1’ during the same clock cycle.

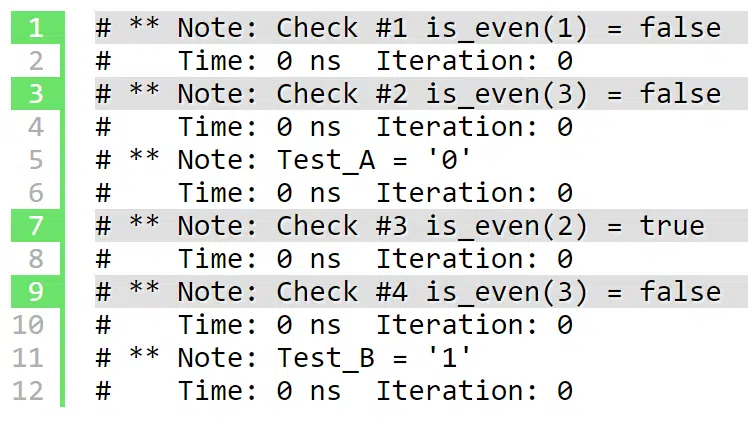

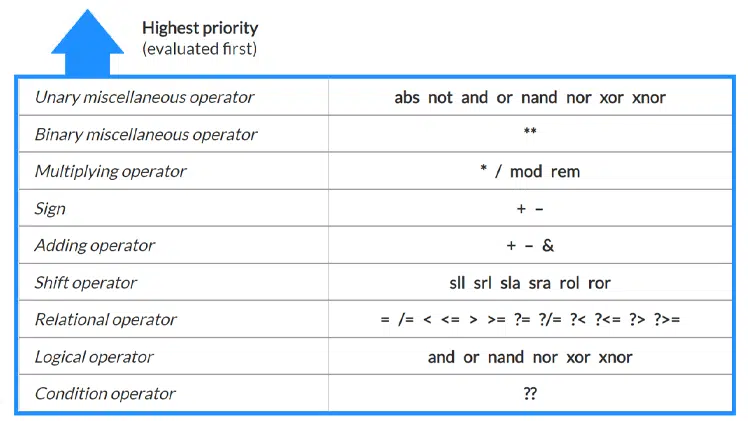

A binary operator is an operator that takes exactly two arguments. Examples of such are addition or multiplication and, of course, the familiar Boolean logical operators we use in VHDL: and, or nand nor xor and xnor.

VHDL groups operators into classes with different precedence levels. Operators are evaluated according to their classes, starting with the highest level. Operators of the same class don’t have any predefined priority. Instead, they are evaluated left to right in the order they appear in the code.

This article shows how to work with strings containing line breaks in VHDL. Read on to learn how to split long lines in your VHDL code, print text containing newline characters, and how VHDL differs from regular programming languages regarding non-printing control characters in strings.

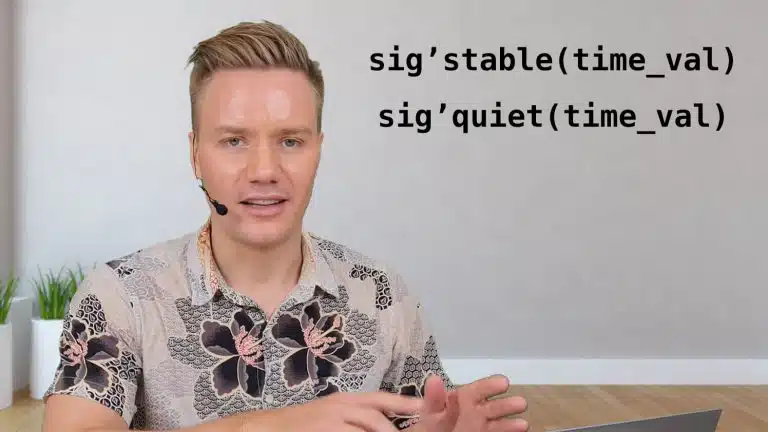

The ‘stable and ‘quiet attributes are predefined in the VHDL standard and work on signal objects. We can use these special features in simulation to check that a signal’s value remains untouched for a given period.

Many people struggle to understand the ModelSim/QuestaSim VHDL simulator’s workflow. I think that’s unnecessary because the basic workflow isn’t hard to learn. I regard the graphical user interface (GUI) as a front-end for the commands listed in this article. For example, when you click the Compile button in the ModelSim GUI, it runs the vcom…

End of content

End of content