I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Interactive testbench using Tcl

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you should always create a self-checking testbench, an interactive testbench can…

How to use a procedure in a process in VHDL

It is possible to drive external signals from a procedure. As long as the signal is within the scope of the procedure, it can be accessed for reading or writing, even if it isn’t listed in the parameter list. Procedures that are declared in the declarative region of the architecture, cannot drive any external signals….

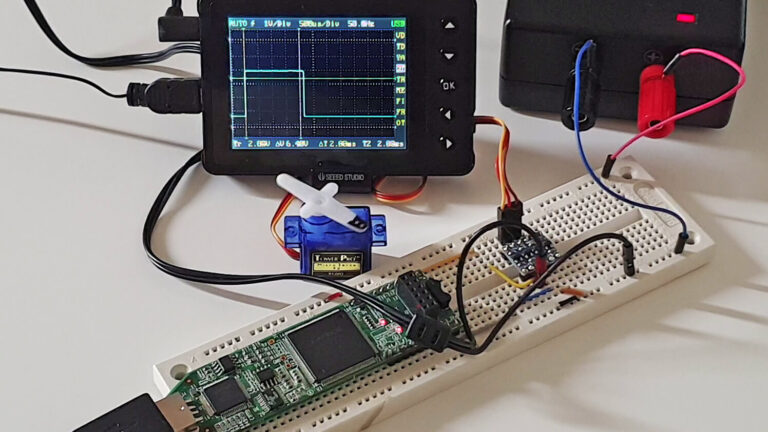

RC servo controller using PWM from an FPGA pin

Radio-controlled (RC) model servos are tiny actuators typically used in hobbyist model planes, cars, and boats. They allow the operator to control the vehicle via a radio link remotely. Because RC models have been around for a long time, the de-facto standard interface is pulse-width modulation (PWM), rather than a digital scheme. Fortunately, it’s easy…

How to create a self-checking testbench

A self-checking testbench is a VHDL program that verifies the correctness of the device under test (DUT) without relying on an operator to manually inspect the output. The self-checking testbench runs entirely on its own, and prints an “OK” or “Failed” message in the end. Every VHDL module should have an associated self-checking testbench. It’s…

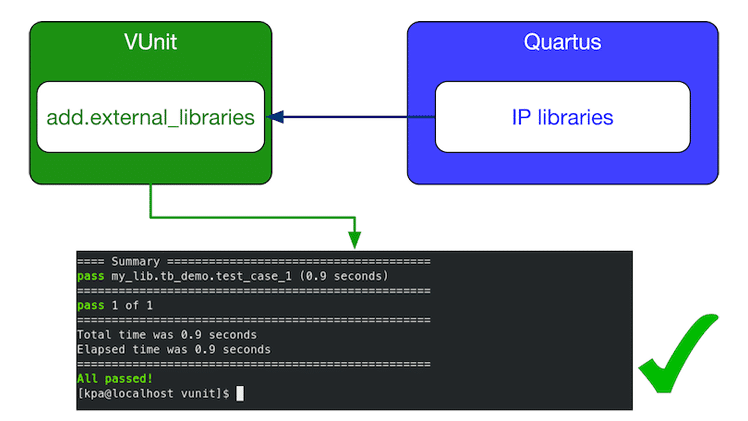

How to link Quartus Prime IP libraries to VUnit

Have you ever wanted to run a VHDL simulation that includes a Quartus IP core through the VUnit verification framework?

This tutorial shows you how to generate, incorporate, and link external Quartus IP libraries to VUnit.

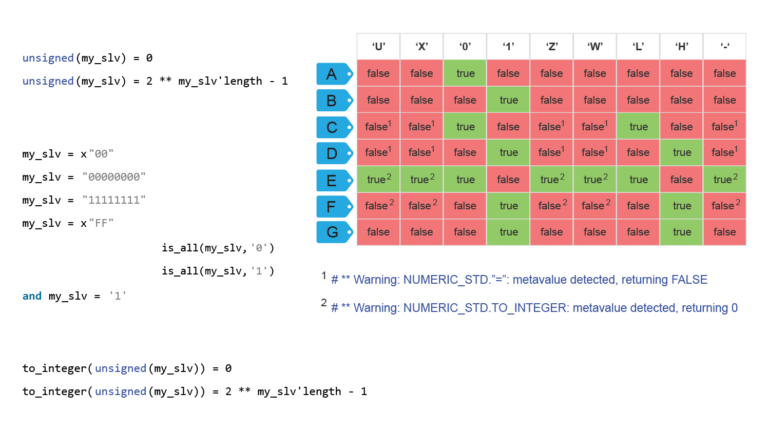

How to check if a vector is all zeros or ones

I know that I have googled this at least a hundred times throughout my career as an FPGA engineer; how to check if all bits in a std_logic_vector signal are ‘0’ or ‘1’. Of course, you know a few ways to do it already, but you want to find the most elegant code that will…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.