I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

How to use a procedure in a process in VHDL

It is possible to drive external signals from a procedure. As long as the signal is within the scope of the procedure, it can be accessed for reading or writing, even if it isn’t listed in the parameter list. Procedures that are declared in the declarative region of the architecture, cannot drive any external signals….

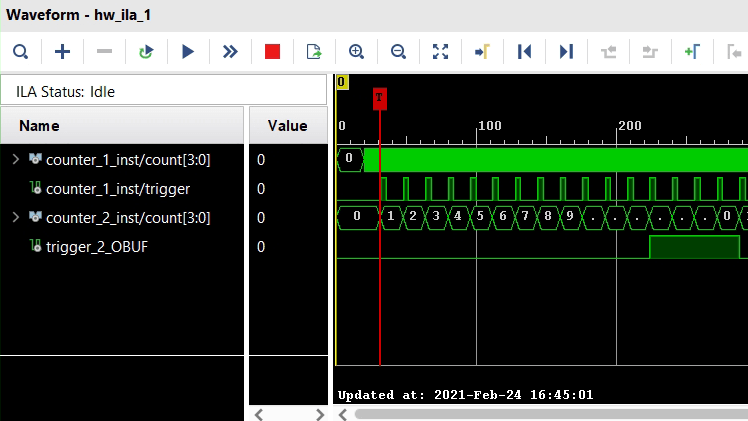

Using Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO)

This tutorial covers using the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor your VHDL design in the Xilinx Vivado IDE. In many cases, designers are in need to perform on-chip verification. That is, gaining access to an internal signal’s behavior in their FPGA design for verification purposes. One option…

How to use a While loop in VHDL

In the previous tutorial, we learned how to use a For-Loop to iterate over an integer range. But what if we want a more detailed control of the loop than just a fixed integer range? We can use a While-Loop for this. The While-Loop will continue to iterate over the enclosed code as long as…

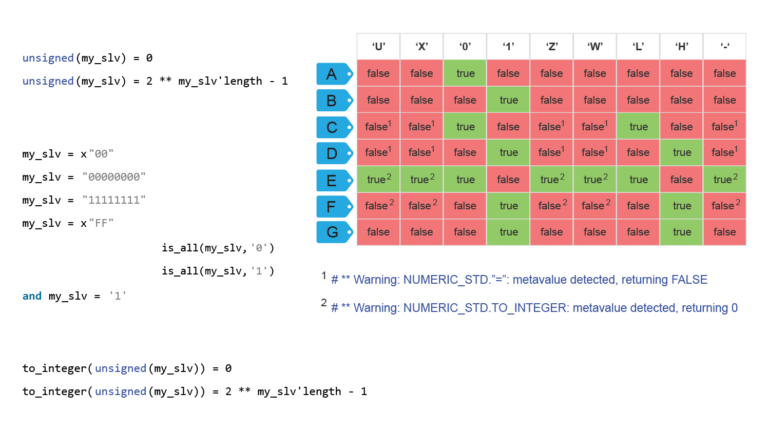

How to check if a vector is all zeros or ones

I know that I have googled this at least a hundred times throughout my career as an FPGA engineer; how to check if all bits in a std_logic_vector signal are ‘0’ or ‘1’. Of course, you know a few ways to do it already, but you want to find the most elegant code that will…

How to use constants and Generic Map in VHDL

Creating modules is a great way to reuse code, but often you need the same module with smaller variations throughout your design. This is what generics and the generic map are for. It allows you to make certain parts of the module configurable at compile-time. Constants are used when we want to avoid typing the…

How to use conditional statements in VHDL: If-Then-Elsif-Else

In the previous tutorial we used a conditional expression with the Wait Until statement. The expression ensured that the process was only triggered when the two counter signals where equal. But what if we wanted the program in a process to take different actions based on different inputs? The If-Then-Elsif-Else statements can be used to…

Though those two codes are logically equivalent, the right one infers a transparent latch, it shouldn’t be used for synthesis.

I don’t think it does, but I’m not 100% sure what the synthesis tools do all the time.

This will infer a latch:

process(InSig) is begin if InSig = '0' then OutSig <= '1'; end if; end process;This shouldn’t create any latches:

process(InSig) is begin OutSig <= '0'; if InSig = '0' then OutSig <= '1'; end if; end process;A link to the question:

https://vhdlwhiz.com/wp-content/uploads/2017/09/quiz_part-2-q6.png

Hi sir, You designed this course very well and advanced. I am happy to recommend this course to my friends.

I’m glad you enjoyed it! And thanks for taking the time to leave a nice comment.