I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

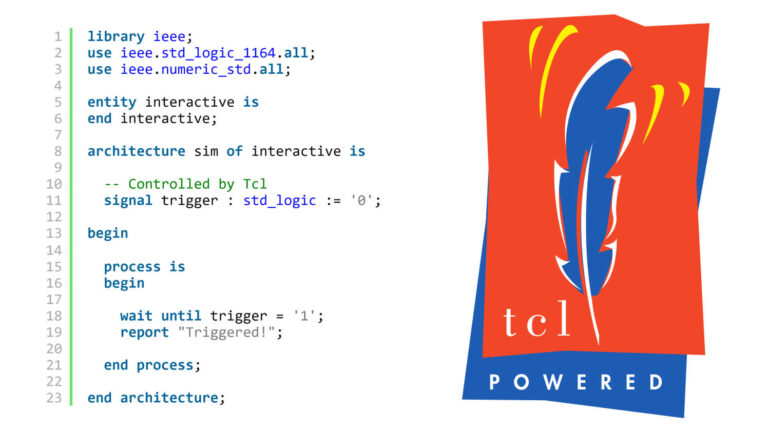

How to create a Tcl-driven testbench for a VHDL code lock module

Most VHDL simulators use the Tool Command Language (Tcl) as their scripting language. When you type a command in the console of the simulator, you are using Tcl. Furthermore, you can create scripts with Tcl that run in the simulator and interact with your VHDL code. In this article, we will create a self-checking testbench…

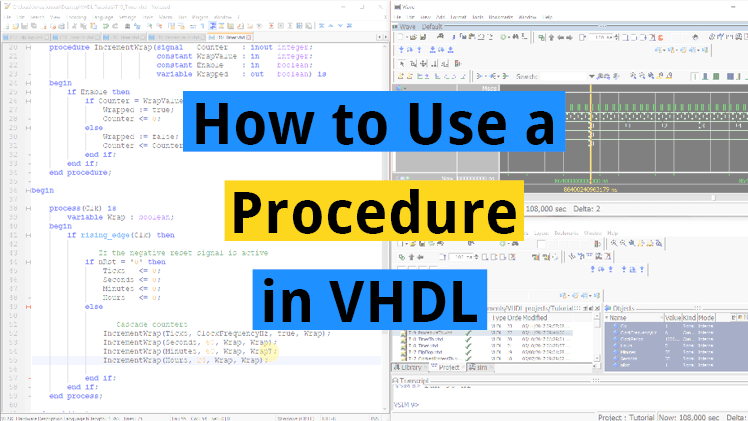

How to use a procedure in VHDL

A procedure is a type of subprogram in VHDL which can help us avoid repeating code. Sometimes the need arises to perform identical operations several places throughout the design. While creating a module might be overkill for minor operations, a procedure is often what you want. Procedures can be declared within any declarative region. The…

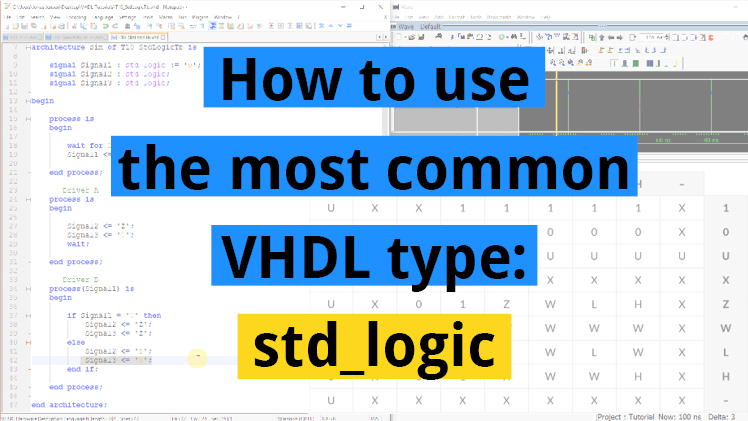

How to use the most common VHDL type: std_logic

The most common type used in VHDL is the std_logic. Think of this type as a single bit, the digital information carried by a single physical wire. The std_logic gives us a more fine-grained control over the resources in our design than the integer type, which we have been using in the previous tutorials. Normally,…

Interactive testbench using Tcl

An interactive testbench is a simulator setup where input to the device under test (DUT) is provided by an operator while the testbench is running. Most often, this would mean you entering commands in the simulator console to provide the DUT with stimulus. While you should always create a self-checking testbench, an interactive testbench can…

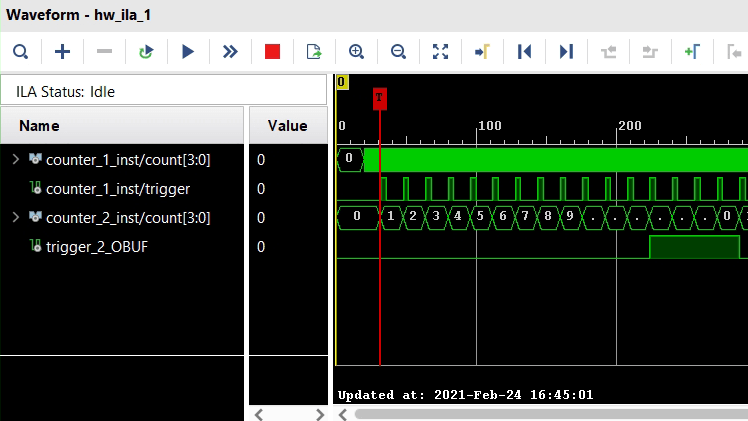

Using Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO)

This tutorial covers using the Integrated Logic Analyzer (ILA) and Virtual Input/Output (VIO) cores to debug and monitor your VHDL design in the Xilinx Vivado IDE. In many cases, designers are in need to perform on-chip verification. That is, gaining access to an internal signal’s behavior in their FPGA design for verification purposes. One option…

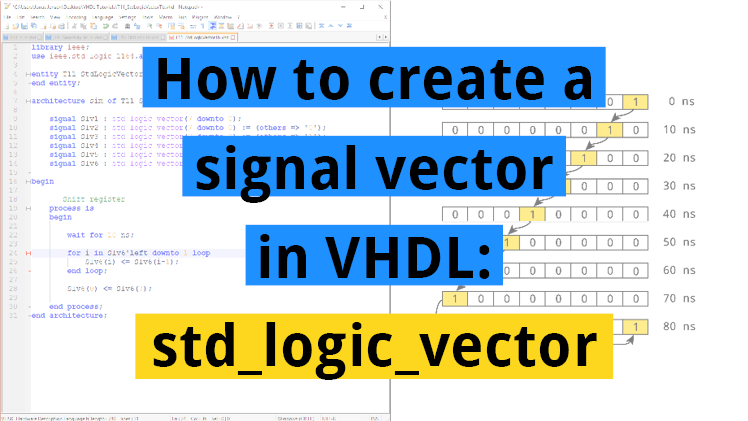

How to create a signal vector in VHDL: std_logic_vector

The std_logic_vector type can be used for creating signal buses in VHDL. The std_logic is the most commonly used type in VHDL, and the std_logic_vector is the array version of it. While the std_logic is great for modeling the value that can be carried by a single wire, it’s not very practical for implementing collections…