I’m from Norway, but I live in Bangkok, Thailand. Before I started VHDLwhiz, I worked as an FPGA engineer in the defense industry. I earned my master’s degree in informatics at the University of Oslo.

Similar Posts

Basic VHDL quiz – Part 2

Test your coding skills with this VHDL quiz after completing tutorials 6-11 from the Basic VHDL Tutorial series!

How to use constants and Generic Map in VHDL

Creating modules is a great way to reuse code, but often you need the same module with smaller variations throughout your design. This is what generics and the generic map are for. It allows you to make certain parts of the module configurable at compile-time. Constants are used when we want to avoid typing the…

How to use a While loop in VHDL

In the previous tutorial, we learned how to use a For-Loop to iterate over an integer range. But what if we want a more detailed control of the loop than just a fixed integer range? We can use a While-Loop for this. The While-Loop will continue to iterate over the enclosed code as long as…

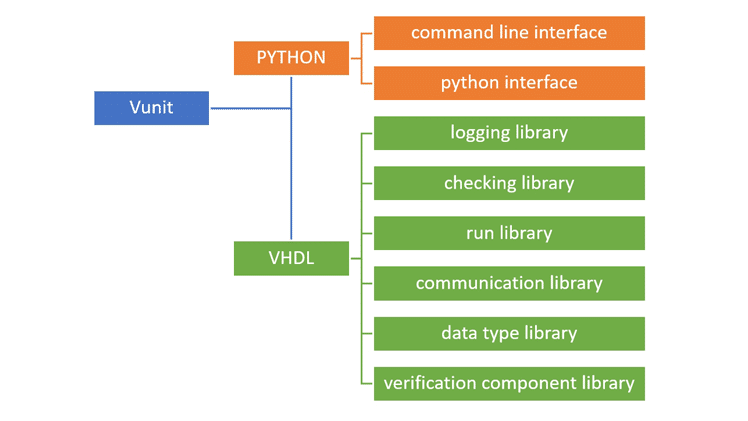

Getting started with VUnit

VUnit is one of the most popular open-source VHDL verification frameworks available today. It combines a Python test suite runner with a dedicated VHDL library to automate your testbenches.

How to create a finite-state machine in VHDL

A finite-state machine (FSM) is a mechanism whose output is dependent not only on the current state of the input, but also on past input and output values. Whenever you need to create some sort of time-dependent algorithm in VHDL, or if you are faced with the problem of implementing a computer program in an…

How to create a Tcl-driven testbench for a VHDL code lock module

Most VHDL simulators use the Tool Command Language (Tcl) as their scripting language. When you type a command in the console of the simulator, you are using Tcl. Furthermore, you can create scripts with Tcl that run in the simulator and interact with your VHDL code. In this article, we will create a self-checking testbench…